【導(dǎo)讀】JESD204B串行數(shù)據(jù)鏈路接口是針對支持更高速轉(zhuǎn)換器不斷增長的帶寬需求而開發(fā)�����。作為第三代標準���,它提供更高的通道速率最大值(每通道高達12.5 Gbps)��,支持確定性延遲和同步幀時 鐘���。此外,JESD204B能輕松傳輸大量待處理的數(shù)據(jù)從而充分利用更高性能的轉(zhuǎn)換器以及與之配合的通用的FPGA�����。

FPGA供應(yīng)商已討論了許多年有關(guān)千兆串行/解串(SERDES)接口的話題��,雖然過去大部分模數(shù)轉(zhuǎn)換器(ADC)和數(shù)模轉(zhuǎn)換器(DAC)并未配備這類高速串行接口����。FPGA和轉(zhuǎn)換器沒有統(tǒng)一的串行接口造 成無法利用SERDES的高帶寬。JESD204B兼容型轉(zhuǎn)換器能夠解決這個問題���,而人們針對這種新功能提出了一些問題�。

什么是8b/10b編碼�,為什么JESD204B接口需使用這種編碼?

無法確保差分通道上的直流平衡信號不受隨機非編碼串行數(shù)據(jù)干擾����,因為很有可能會傳輸大量相反的1或0數(shù)據(jù)。通過串行鏈路傳輸?shù)碾S機數(shù)據(jù)還可能長時間無活動狀態(tài),并在相對較長的時間內(nèi)為全1或全0����。

發(fā)生這種情況時,未編碼串行數(shù)據(jù)流的直流平衡會偏向高電平或低電平兩種極端情況中的一種�。此時,若鏈路上再次傳輸有效數(shù)據(jù)�,則很有可能發(fā)生位錯誤�����,因為線路需重新建立偏置����。 另外,一個長期的問題是電子遷移��,因為差分對的一路長期保持對另一路的固定點評�。為了克服這些問題,通常在差分串行數(shù)據(jù)流中(包括JESD204B)采用8b/10b編碼方案�。

8b/10b編碼采用10個數(shù)據(jù)位,通過查找表方式從源端發(fā)送器發(fā)送8位初始信息����。這種方式具有25%的固有開銷(10b/8b = 1.25),效率較低。此外����,編碼允許每個10位符號傳輸至少3位(但不 超過8位)數(shù)據(jù)。這樣可確保接收器有足夠的轉(zhuǎn)換數(shù)據(jù)來恢復(fù)內(nèi)嵌的時鐘信息�����,而無論底層數(shù)據(jù)的動態(tài)活動狀態(tài)如何�。

使用8b/10b編碼時,串行數(shù)據(jù)流中二進制0和1之間的偏差保持在±1以內(nèi)�,因此信號長期保持直流平衡。然后����,必須在接收器端的數(shù)據(jù)流上執(zhí)行10位到8位的反向解碼,才能利用反向查找 表恢復(fù)原始數(shù)據(jù)���。更為高效的64b/66b編碼工作原理與此相似���,但開銷僅為3.125%。這種方式更為先進����,可能會用于未來的JESD204發(fā)布版中����。

我為轉(zhuǎn)換器分配的JESD204B通道在系統(tǒng)板上無法順利路由至FPGA����。交叉對太多,非常容易受串擾影響�����。能否重新映射JESD204B的通道分配�����,改善布局���?

雖然轉(zhuǎn)換器的JESD204B串行通道可能由數(shù)字、字母或其他術(shù)語指定其完整鏈路的特定關(guān)系��,但這種關(guān)系并非一定要保持固定不變���。規(guī)范允許在初始配置數(shù)據(jù)中重新映射分配關(guān)系��,只要每 個通道和器件都有獨特的識別號即可����。鏈路配置數(shù)據(jù)包含器件和通道識別號,可識別其操作����。利用該信息,通過縱橫式多路復(fù)用器��,多通道發(fā)送器就可方便地重新分配任何數(shù)字邏輯串行數(shù)據(jù)至任何物理輸出通道�����。

雖然這只是規(guī)范許可的一個可選功能�����,但如果ADC供應(yīng)商提供縱橫式多路復(fù)用器功能��,可將邏輯輸出重新分配給物理輸出���,那么鏈路I/O就能重新配置為最佳順序�����,為布局布線提供最大程 度的便利�����。FPGA接收器可接收相同的初始配置數(shù)據(jù)��,并改變預(yù)期通道分配�,恢復(fù)數(shù)據(jù)。有了這一功能�����,從一個器件到另一個器件的通道路由便簡單得多����,并可獨立于硅片供應(yīng)商在數(shù)據(jù)手冊中分配的初始名稱。

我正嘗試在我系統(tǒng)中設(shè)計一個使用JESD204B多點鏈路的轉(zhuǎn)換器�����。它與單點鏈路有何不同��?

JESD204B規(guī)范提供稱為“多點鏈路”的接口���。它是一種連接三個或三個以上JESD204B設(shè)備的通信鏈路。取決于轉(zhuǎn)換器的使用方式���,相比單點鏈路���,這種鏈路配置在某些情況下更為有效��。

比如�����,使用JESD204B的雙通道ADC����。大部分情況下�,雙通道ADC針對兩個轉(zhuǎn)換器提供單個時鐘輸入。它將迫使ADC以同樣的頻率進行模擬采樣�。但對于某些特定的應(yīng)用而言,這類器件也可能采用兩個獨立的輸入時鐘�,每個時鐘可單獨驅(qū)動對應(yīng)的ADC。這樣����,兩個ADC之間便有可能產(chǎn)生采樣相位差,甚至每個ADC單獨以相互不相干的頻率進行采樣����。在后一種情況中�����,單個JESD204B鏈路上存在來自所有兩個轉(zhuǎn)換器的數(shù)據(jù)����,若不采用復(fù)雜的后端FIFO方案�,則無法正常工作。

該問題的一種解決方案是讓雙通道轉(zhuǎn)換器使用多點鏈路JESD204B接口�,其中每個轉(zhuǎn)換器都使用各自獨立的串行鏈路輸出。然后便可針對每個ADC使用非相干時鐘�����,且每個串行鏈路的輸出可方 便地單獨路由至獨立的FPGA或ASIC����。多點鏈路配置還可用于將單個FPGA的多路數(shù)據(jù)流發(fā)送至多個DAC。隨著鏈路上器件數(shù)目的增加����,在多點配置中最小化器件的時鐘分布偏斜將會是非常具有 挑戰(zhàn)性的任務(wù)�。

JESD204B中的確定延遲到底是什么?它是否就是轉(zhuǎn)換器的總延遲����?

ADC的總延遲表示其輸入一個模擬樣本����、處理�����、并從器件輸出數(shù)字信號所需的時間�。類似地,DAC的總延遲表示從數(shù)字樣本數(shù)據(jù)輸入器件直到模擬輸出相應(yīng)樣本的時間��。通常�,對這兩者都以分辨率為采樣時鐘周期進行測量,因為它們與頻率有關(guān)����。這在原理上與JESD204B鏈路部署中描述的確定延遲的定義有所不同。

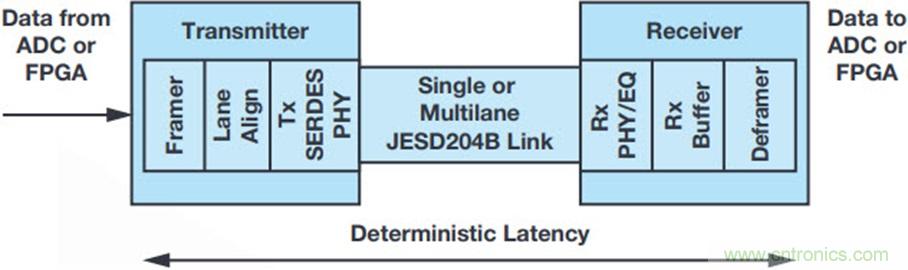

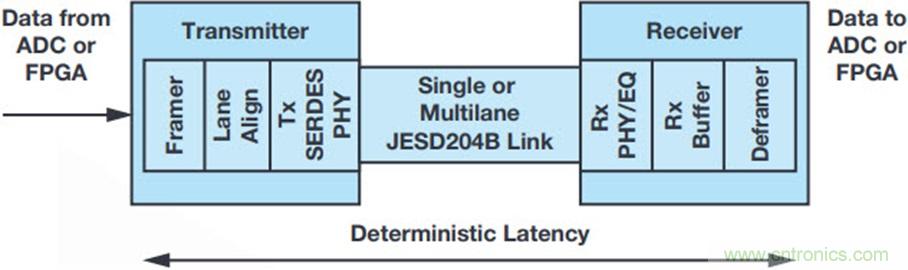

JESD204B鏈路的確定延遲定義為數(shù)據(jù)從發(fā)送器(ADC或源端FPGA)的并行幀數(shù)據(jù)輸入傳播至接收器(DAC或接收端FPGA)并行解幀數(shù)據(jù)輸出所需的時間�。該時間通常以分辨率為幀時鐘周期或以器件時鐘進行測量(圖1)。該定義不包括ADC的模擬前端內(nèi)核或DAC的后端模擬內(nèi)核�。不僅兩個器件在這種延遲計算中作為函數(shù)使用,與兩個器件接口的串行數(shù)據(jù)信號路由也將作為函數(shù)參與計算��。這意味著確定延遲在多轉(zhuǎn)換器系統(tǒng)或多點鏈路中,可能大于或小于確定延遲�����,具體取決于JESD204B通道的路由長度�。接收器的緩沖器延遲有助于彌補路由造成的延遲差異。

圖1. 兩個互連器件的幀封裝器與去幀器之間JESD204B確定性延遲的概念示例����。延遲是三個項目的函數(shù):發(fā)射器、接收器和兩者之間的接口傳播時間����。

JESD204B如何使用結(jié)束位?結(jié)束位存在的意義是什么��?

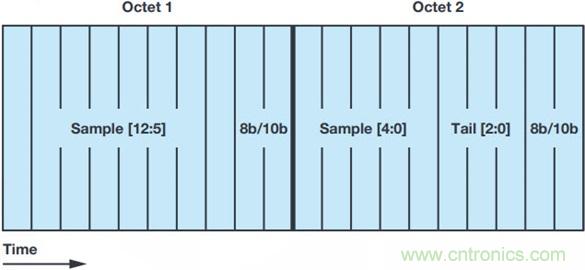

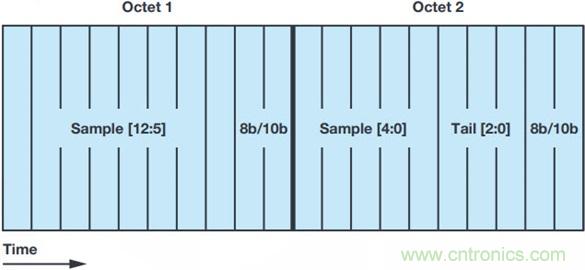

JESD204B鏈路允許分配多于實際需要的信息空間����,用來發(fā)送轉(zhuǎn)換器數(shù)據(jù)和控制位。如果某個特定轉(zhuǎn)換器或配置的數(shù)據(jù)未填滿整個空間��,則以定義中的結(jié)束位填充����。例如��,N'''''''''''''''' = 16的空間大 于打包后的13位實際數(shù)據(jù)(N = 13 + CS = 0)。這種情況下��,將使用3個結(jié)束位填充未使用的數(shù)據(jù)空間(圖2)�����。

圖2. 若轉(zhuǎn)換器僅使用13位采樣數(shù)據(jù)�����,則3個結(jié)束位可用于補充N’ = 16的第二個8位字�。

結(jié)束位是無信息內(nèi)容的偽數(shù)據(jù)位,僅用于發(fā)射器完全填充未使用的空間�����。如果以重復(fù)靜態(tài)值填充結(jié)束位���,它們可能會產(chǎn)生干擾雜散噪聲�����;但也可用來代表偽隨機序列�。發(fā)射器和接收器都 必須根據(jù)鏈路配置了解這些位不含信息,從而接收器可方便地將它們從相關(guān)數(shù)據(jù)流中去除��。

我的鏈路模式?jīng)]有任何問題�,但在正常工作模式下發(fā)送器不發(fā)送數(shù)據(jù)。在歷代轉(zhuǎn)換器中��,低壓差分信號(LVDS)和并行接口允許對DAC或ADC的最低有效位(LSB)或最高有效位(MSB)進行簡單探測/調(diào)試���,檢查函數(shù)轉(zhuǎn)換器是否正在工作�。使用JESD204B接口時如何探測MSB或LSB��?

這是JESD204B接口的少數(shù)幾個弊端之一��。對LSB或MSB I/O進行電探測以便查看轉(zhuǎn)換器兩個方向的鏈路上是否存在正確的活動并不容易�����。這是因為����,采樣數(shù)據(jù)以通道為單位進行串行化,因此 無法輕易電探測特定的加權(quán)數(shù)據(jù)位����。然而����,如果您希望快速了解轉(zhuǎn)換器是否正在發(fā)送或接收任何有效數(shù)據(jù)(如果確實存在這些數(shù)據(jù)的話)��,那么依然可以采用某些方法實現(xiàn)���。

某些示波器供應(yīng)商提供實時數(shù)據(jù)處理以便串行解碼8b/10b數(shù)據(jù),并在示波器屏幕上顯示未編碼數(shù)據(jù)流���。采用這種方法可以探測未加擾數(shù)據(jù)�����,從而確定鏈路上正在進行何種活動�。

FPGA供應(yīng)商提供內(nèi)部探測軟件工具�����,通過一個USB加密狗將其與計算機相連�����,為系統(tǒng)設(shè)計人員提供一種觀察FPGA內(nèi)發(fā)送和接收I/O數(shù)據(jù)的方法�����。另外,某些ASIC和轉(zhuǎn)換器提供內(nèi)部串行回送 自測模式�,可用于辨認鏈路上的數(shù)據(jù)問題。

假設(shè)其他鏈路參數(shù)已知�����,如何計算轉(zhuǎn)換器的通道速率��?

如果已知轉(zhuǎn)換器�����、ASIC或FPGA的其他關(guān)鍵參數(shù)���,則使用JESD204B的系統(tǒng)設(shè)計人員能方便地計算出鏈路的通道數(shù)或通道速率�。所有基本鏈路參數(shù)都有如下所示的數(shù)學(xué)關(guān)系��,可以據(jù)此計算未知 變量����。根據(jù)計算結(jié)果,系統(tǒng)設(shè)計人員能夠在轉(zhuǎn)換器或FPGA限定的架構(gòu)內(nèi)選擇其他參數(shù)�����,改變鏈路操作。

其中:

M表示鏈路上轉(zhuǎn)換器的數(shù)量����。

N’表示一個樣本內(nèi)發(fā)送的信息位的數(shù)量(包括樣本分辨率、控制和結(jié)束位)�����。

fs是器件或采樣時鐘��。

L表示通道數(shù)����。

通道速率表示單個通道的位速率���。

10/8表示8b/10b編碼的鏈路開銷���。

例如,考慮雙通道ADC的情況:N’ = 16����,fs = 235 MHz,使用兩個通道���。什么是通道速率?

什么是應(yīng)用層����,它能做什么?

應(yīng)用層是JESD204B提供的一種方法���,允許樣本數(shù)據(jù)映射到普通規(guī)格之外��。這對于某些需要傳送數(shù)據(jù)樣本尺寸不同于鏈路N''''''''''''''''的轉(zhuǎn)換器模式而言非常有用��。

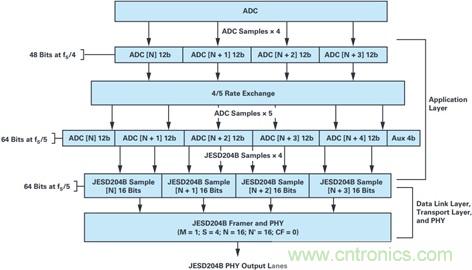

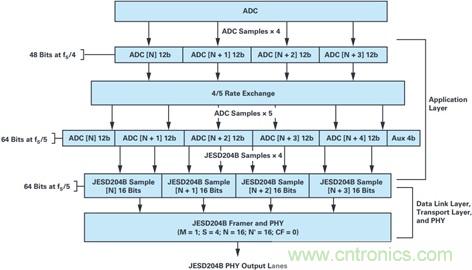

使用應(yīng)用層����,可將鏈路上原本通道數(shù)較低或通道速率較小的低效率配置變得更為高效��。發(fā)射器和接收器都需要進行配置才能了解特定的應(yīng)用層����,因為特定的轉(zhuǎn)換器模式會定制或有針對性 地對應(yīng)用層進行設(shè)計。圖3顯示了一個示例�,其中5個樣本被分配到通常僅能為4個樣本所占據(jù)的空間。

圖3. ADC應(yīng)用層可將5個12位ADC樣本重新映射到4個JESD204B N’ = 16樣本所用空間中�����。4位額外輔助信息可提供其他用途。

使用上一個問題中的等式進行應(yīng)用層計算時�,需使用有效N''''''''''''''''而非實際N''''''''''''''''。例如�,下文所示的應(yīng)用層示例中,雖然實際的JESD024B樣本N''''''''''''''''參數(shù)為16�,但可算出ADC樣本的有效N'''''''''''''''',因為該例中以64位發(fā)送5個樣本���。因此���,NEFF = 64/5 = 12.8���。由于其他變量保持不變��,通道速率將下降20%:

前景如何��?

隨著JESD204B在數(shù)據(jù)轉(zhuǎn)換器市場上的不斷普及�����,F(xiàn)PGA平臺上具有知識產(chǎn)權(quán)(IP)的功能將有助于其推廣應(yīng)用��。雖然這項技術(shù)更為復(fù)雜���,但由于更多的工程師開始使用JESD204B來設(shè)計新系統(tǒng)��, 未來有關(guān)這一話題的討論還將繼續(xù)����。

推薦閱讀: