【導(dǎo)讀】多通道加電和斷電排序已經(jīng)成為很多電源系統(tǒng)的必備功能。隨著這些系統(tǒng)的復(fù)雜度不斷增加,工程師必須針對更加嚴(yán)密緊湊的計時技術(shù)規(guī)格進行設(shè)計,并且在反向序列出現(xiàn)時具有斷電功能,并且能夠處理大量的電源軌。

LM3880/LM3881簡單電源排序器提供一個簡單且精準(zhǔn)的方法,來控制這3個獨立電源軌的加電和斷電—然而,根據(jù)目前電源系統(tǒng)所具有的復(fù)雜度來看,3通道排序也許還是不夠用。所以,對于那些需要對更多電源軌進行排序的系統(tǒng),你可以將兩個LM3880/LM3881器件級聯(lián)在一起,以實現(xiàn)6通道電源排序。在這篇博文中,我將討論一下如何將這些器件級聯(lián)在一起,實現(xiàn)所需應(yīng)用。

針對3通道排序的單個LM3880

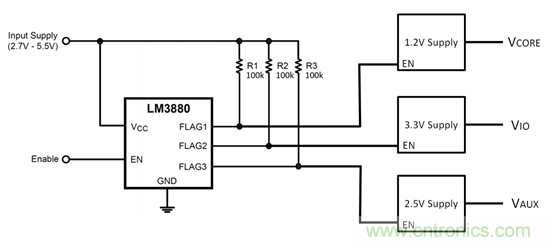

LM3880通常用于3個電源的加電和斷電排序,并且在寬溫度范圍內(nèi),借助精密時序功能來提供一個非常簡單的解決方案。這一點在斷電過程中需要反向序列時特別重要;這種情況會出現(xiàn)在很多微處理器和現(xiàn)場可編程門陣列 (FPGA) 中。圖1顯示了一個LM3880使用示例;在加電和斷電期間,需要以正確加電序列,按照順序?qū)σ粋€FPGA的VCORE, VIO 和 VAUX 加電。

圖1:使用LM3880時的3通道電源排序

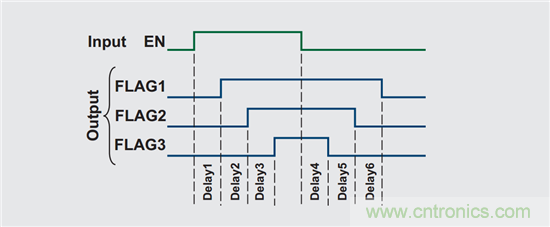

圖2顯示的是加電和斷電期間的時序圖。在這個示例中,3個FPGA電源將被啟用,從VCORE 開始,每隔30ms的時間;斷電時,順序相反,從VAUX開始。而工程師們常常忽略的是,為了防止雜散電流路徑的出現(xiàn),比如說流經(jīng)一個FPGA的內(nèi)部P-N結(jié),反向斷電順序與加電順序同樣重要。因此,正確排序?qū)⒃黾咏K端產(chǎn)品的使用壽命,并且提升產(chǎn)品可靠性。

圖2: 3通道時序圖

針對6通道排序的2個LM3880

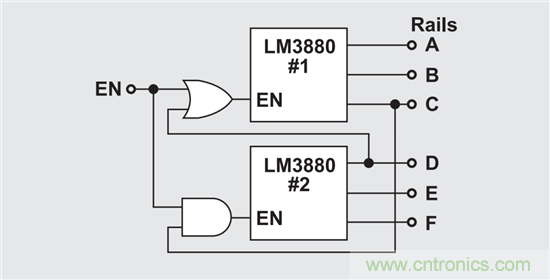

對于需要的電源軌多于3個應(yīng)用該怎么辦呢?有沒有一個簡單的方法對這些系統(tǒng)進行排序呢?謝天謝地,還真有!你可以將2個LM3880集成電路 (IC) 級聯(lián)在一起,以實現(xiàn)6通道加電和斷電排序,除此之外,只需要一個外部AND門和OR門。圖3顯示的是這一應(yīng)用的經(jīng)簡化示例,其中的上拉電阻器被省略掉了。

圖3:使用2個LM3880時的6通道電源排序

這個級聯(lián)系統(tǒng)配置是如何工作的?

加電時,OR門確保1號LM3880被EN上升邊緣觸發(fā),而且電源軌A、B和C開始按順序加電。AND門確保2號LM3880在它收到一個EN信號,并且電源軌C被觸發(fā)之前不會被觸發(fā)。

斷電時,AND門確保2號LM3880可以偵測到EN下降邊緣,并且電源軌F、E和D按順序斷電。OR門確保第一排序器在D已經(jīng)下降前不會偵測到EN下降邊緣。

針對級聯(lián)系統(tǒng)配置的主要設(shè)計注意事項

在選定AND門和OR門時,以下是一些主要注意事項:

● AND門和OR門輸出的擺幅范圍應(yīng)該足夠大,這樣的話,LM3880的EN閥值可以在上升和下降邊緣上觸發(fā)。

● 對于兩個LM3880 IC,以及AND門和OR門來說,最好使用同樣電源。

● LM3880 IC的標(biāo)志輸出必須能夠觸發(fā)上升和下降邊緣上的AND門和OR門輸入。這意味著,在選定AND門和OR門時,你必須考慮他們的輸入閥值,以及它們所具有的任何遲滯,并且確保LM3880標(biāo)志輸出的邏輯電平能夠觸發(fā)邏輯門的輸入閥值。

正是由于我在上文中提到的原因,LM3880簡單電源排序器提供易于使用且準(zhǔn)確的解決方案,實現(xiàn)多達6個電源軌的排序??紤]到當(dāng)前非常嚴(yán)密緊湊的時序要求,以及對于反向斷電排序的需要,不會有比這個解決方案更簡單的解決方案了。

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請聯(lián)系小編進行處理。

推薦閱讀: