【導讀】采用這種結構的PLD芯片有:Altera的MAX7000,MAX3000系列(EEPROM工藝),Xilinx的XC9500系列(Flash工藝)和Lattice,Cypress的大部分產品(EEPROM工藝)。

一.基于乘積項(Product-Term)的PLD結構

采用這種結構的PLD芯片有:Altera的MAX7000,MAX3000系列(EEPROM工藝),Xilinx的XC9500系列(Flash工藝)和Lattice,Cypress的大部分產品(EEPROM工藝)

我們先看一下這種PLD的總體結構(以MAX7000為例,其他型號的結構與此都非常相似):

圖1 基于乘積項的PLD內部結構

這種PLD可分為三塊結構:宏單元(Marocell),可編程連線 (PIA)和I/O控制塊。 宏單元是PLD的基本結構,由它來實現基本的邏輯功能。圖1中蘭色部分是多個宏單元的集合(因為宏單元較多,沒有一一畫出)??删幊踢B線負責信號傳遞,連 接所有的宏單元。I/O控制塊負責輸入輸出的電氣特性控制,比如可以設定集電極開路輸出,擺率控制,三態(tài)輸出等。 圖1 左上的INPUT/GCLK1,INPUT/GCLRn,INPUT/OE1,INPUT/OE2 是全局時鐘,清零和輸出使能信號,這幾個信號有專用連線與PLD中每個宏單元相連,信號到每個宏單元的延時相同并且延時最短。

宏單元的具體結構見下圖:

圖2 宏單元結構

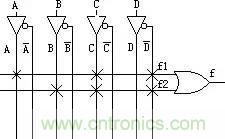

左側是乘積項陣列,實際就是一個與或陣列,每一個交叉點都是一個可編程 熔絲,如果導通就是實現“與”邏輯。后面的乘積項選擇矩陣是一個“或”陣列。兩者一起完成組合邏輯。圖右側是一個可編程D觸發(fā)器,它的時鐘,清零輸入都可 以編程選擇,可以使用專用的全局清零和全局時鐘,也可以使用內部邏輯(乘積項陣列)產生的時鐘和清零。如果不需要觸發(fā)器,也可以將此觸發(fā)器旁路,信號直接 輸給PIA或輸出到I/O腳。

二.乘積項結構PLD的邏輯實現原理

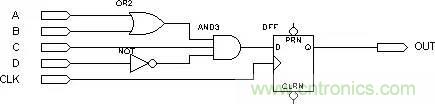

下面我們以一個簡單的電路為例,具體說明PLD是如何利用以上結構實現邏輯的,電路如下圖:

圖3

假設組合邏輯的輸出(AND3的輸出)為f,則f=(A+B)*C*(!D)=A*C*!D + B*C*!D ( 我們以!D表示D的“非”)

PLD將以下面的方式來實現組合邏輯f:

圖4

A,B,C,D由PLD芯片的管腳輸入后進入可編程連線陣列 (PIA),在內部會產生A,A反,B,B反,C,C反,D,D反8個輸出。圖中每一個叉表示相連(可編程熔絲導通),所以得到:f= f1 + f2 = (A*C*!D) + (B*C*!D) 。這樣組合邏輯就實現了。 圖3電路中D觸發(fā)器的實現比較簡單,直接利用宏單元中的可編程D觸發(fā)器來實現。時鐘信號CLK由I/O腳輸入后進入芯片內部的全局時鐘專用通道,直接連接 到可編程觸發(fā)器的時鐘端??删幊逃|發(fā)器的輸出與I/O腳相連,把結果輸出到芯片管腳。這樣PLD就完成了圖3所示電路的功能。(以上這些步驟都是由軟件自 動完成的,不需要人為干預)

圖3的電路是一個很簡單的例子,只需要一個宏單元就可以完成。但對于一個復雜的電路,一個宏單元是不能實現的,這時就需要通過并聯擴展項和共享擴展項將多個宏單元相連,宏單元的輸出也可以連接到可編程連線陣列,再做為另一個宏單元的輸入。這樣PLD就可以實現更復雜邏輯。

這種基于乘積項的PLD基本都是由EEPROM和Flash工藝制造的,一上電就可以工作,無需其他芯片配合。