【導讀】隨著電路板上走線密度越來越高,信號串擾總是一個難以忽略的問題。因為不僅僅會影響電路的正常工作,還會增加電路板上的電磁干擾。

在電路板上的一些高頻信號會串擾到MCU電路或者MCU的I/O接口電路,形成共模電壓,眾所周知,共模電壓在電路設(shè)計時是最讓人討厭的玩意兒,因此,設(shè)計電路板時要避免各種可能造成電路工作不正常的共模電壓的串擾。

減小電路板上串擾的設(shè)計原則簡單歸類

1,通過合理布局使各個元器件之間的連線盡量短。

2,由于串擾程度和施加干擾信號的頻率成正比,因此要使高頻信號線遠離敏感信號線。

3,施加干擾信號線與受到干擾信號線不僅要遠離,最好要用地線隔離,并且避免相互平行走線。

4,在多層PCB板中,施加干擾信號線與受到干擾信號線或敏感信號走線要用地線隔離或相隔地層。

5,在多層PCB板中,施加干擾信號線與受到干擾信號線分別在地線或地層的相對兩面,也就是隔層。

6,盡量使用輸入阻抗較低的敏感電路,必要時可以使用旁路電容降低敏感電路的輸入阻抗。

最后注意的是,在布線時,地線對于抑制信號串擾的作用是非常明顯的,在干擾線和受干擾線直接布地線,可以將串擾降低10db左右。

著名的3W布線規(guī)則

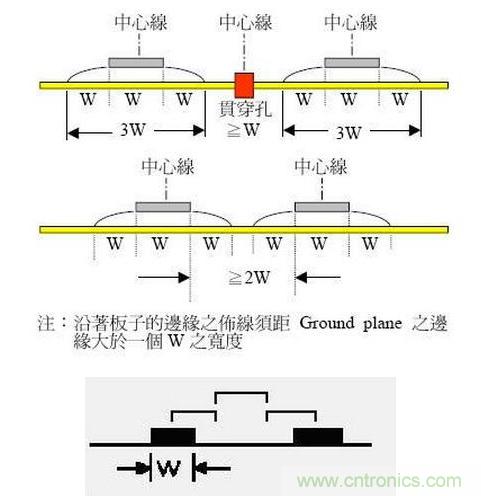

在抑制電路板走線信號串擾方面,有一個非常有名的3W布線規(guī)則(其中W就是布線寬度),它的內(nèi)容是:對于寬度是3W的信號線,如果其他走線的中心和它的中心之間的距離大于3W,就能避免信號之間的串擾。如下圖所示。

根據(jù)這個規(guī)則,3W范圍內(nèi)包含了信號電流產(chǎn)生的75%的磁通量,只要相鄰的導線在這個范圍之外,信號之間的串擾就不會很嚴重,值得注意的是,信號電流產(chǎn)生的磁通量的98%包含在10W范圍內(nèi)。