【導讀】大型時鐘樹使用多種類型的傳輸線,跨越多塊電路板和多條同軸電纜,通過多個時鐘器件路由時鐘信號的情況并不少見。即使采用最佳實踐做法,這些介質(zhì)中的任何一種都可能帶來大于10 ps的相位偏差。

簡介

大型時鐘樹使用多種類型的傳輸線,跨越多塊電路板和多條同軸電纜,通過多個時鐘器件路由時鐘信號的情況并不少見。即使采用最佳實踐做法,這些介質(zhì)中的任何一種都可能帶來大于10 ps的相位偏差。然而,在一些應用中,需要所有時鐘信號實現(xiàn)小于1 ps的偏差。其中一些應用包括相控陣、MIMO、雷達、電子戰(zhàn)(EW)、毫米波成像、微波成像、儀表和軟件定義無線電(SDR)。

本文指出了設計過程、制造過程和應用環(huán)境中可能導致1 ps或以上相位偏差的幾個關(guān)切問題。對于這些關(guān)切問題,本文將提供一些建議、示例和經(jīng)驗法則,幫助讀者直觀地了解相位偏差的根本原因和幅度。

傳輸線的延遲等式

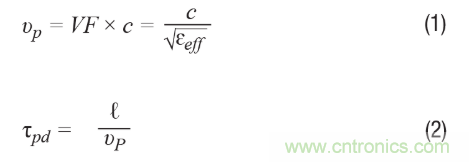

這里列出的等式用于估算單個時鐘路徑的傳播延遲(τ pd)和由于多個時鐘傳播途徑或環(huán)境條件變化導致的傳播延遲的變化值在大型時鐘樹應用中,時鐘走線之間的Δτpd是總系統(tǒng)時鐘偏移的一部分。等式1和等式2提供了兩個主變量,它們用于控制一條傳輸線的τpd:傳輸線的物理長度(?)和有效介電常數(shù)(? eff)。對于等式1,vp表示傳輸線相速度,VF表示速度因子(%),c表示光速(299,792,458 m/s)。

等式3計算兩條傳輸線之間的增量傳播延遲 (?τpd)

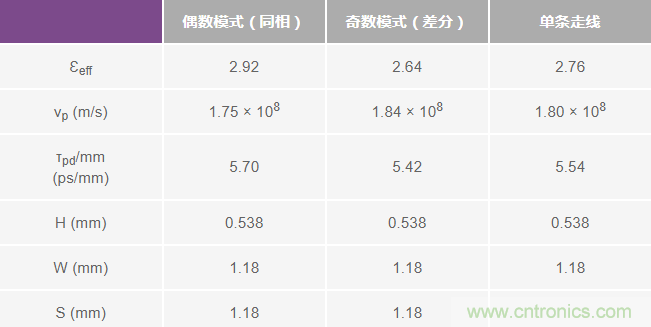

傳輸線介電材料具有隨溫度而變化的特性。介電常數(shù)的溫度系數(shù)(TCDk)通常用相位變化(Δ?ppm)與溫度的關(guān)系曲線表示,單位為百萬分之一(ppm);其中Δ?ppm值為目標溫度下的相位與基準溫度(通常為25°C)下的相位的差值。已知溫度,Δ?ppm和傳輸線長度時,等式4用于估算傳播延遲相對于基準溫度的變化。

同軸電纜介電材料具有因電纜彎曲而改變的特性。電纜彎曲的半徑和角度決定了有效介電常數(shù)的變化。一般地,通過比較特定電纜彎曲的相位與直線電纜的相位,將其表示為相位的變化(Δ?deg)。對于已知Δ?deg、信號頻率(f)和電纜彎曲,等式5用于估算傳播延遲的變化。

延遲變化注意事項

傳輸線的選擇

建議: 為了在多條走線之間獲得最佳延遲匹配效果,就要匹配走線長度和傳輸線類型。

經(jīng)驗法則:

兩條走線長度之間相差1mm,就相當于Δτpd ~6 ps(兩個走線長度之間相差6mil就相當于Δτpd ~1 ps)。

帶狀線比微帶線或?qū)w背襯的共面波導(CB-CPW)慢約1 ps/mm。

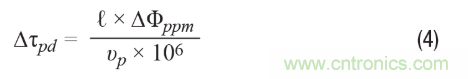

不同的傳輸線類型會產(chǎn)生不同的?eff和vp。使用等式2,這意味著物理長度相同的不同傳輸類型則有不同的τpd。表1和圖1提供了三種常見傳輸線(CB-CPW、微帶線和帶狀線)的仿真結(jié)果,凸顯了?eff、vp和τpd之間的差異。該仿真估算得到,對于10厘米的CB-CPW走線,τpd比相同長度的帶狀線走線大100 ps。仿真是用Rogers Corporation的微波阻抗計算器(Microwave Impedance Calculator)生成的。

表1. 圖1中的Rogers 4003C仿真結(jié)果

Rogers 4003C的相對磁導率(?r),也稱為介電常數(shù)(Dk),為3.55。注意,在表1中,CB-CPW和微帶線的?eff較低,因為它們暴露在空氣之下,而空氣的?r = 1。

要在同一層或者用同一種類型的傳輸線來對那些要求延時匹配的信號進行走線并不是總能實現(xiàn)的。表2提供了在為不同走線選擇傳輸線類型時需要考慮的一些通用因素。如果需要匹配不同傳輸線類型的τpd,最好使用電路板仿真工具而不是手動計算和經(jīng)驗法則。

表2. 廣義傳輸線的考慮因素

圖1. 匹配傳輸線類型。

傳輸線過孔

建議: 如果信號路徑有過孔,請記住在計算傳播延遲時,要考慮兩個目標信號層之間的過孔長度。

若只是粗略計算傳播延遲,假設連接兩個信號層的過孔長度在相位速度上與傳輸線相同。例如,連接62mil厚板的頂部和底部信號層的過孔將占額外的τpd ~10ps。

相鄰走線、差分信號和單端信號

建議: 在走線之間保持最少一個線寬度,避免在 ?eff出現(xiàn)顯著變化。

經(jīng)驗法則:

100 Ω差分信號(奇模式)比50 Ω單端信號快。

密集的同相50 Ω單端信號(偶模式)比單個50 Ω單端信號慢。

密集相鄰走線的信號方向會改變?eff,并且因而會改變等長走線之間的延遲匹配。圖2和表3中提供了兩個邊緣耦合微帶線走線與單個微帶線走線的仿真情況。該仿真估計,兩個10厘米邊緣耦合偶數(shù)模式走線的τpd比等長獨立單個走線大16 ps。

當嘗試將單端τpd與差分τpd匹配時,重要的是仿真兩條路徑的相位速度。在時鐘應用中,當嘗試發(fā)送與差分參考或時鐘信號時間對齊的CMOS同步或SYSREF請求信號時,可能會出現(xiàn)這種情況。增加差分信號路徑之間的間隔會在差分信號和單端信號之間產(chǎn)生更接近的相位速度匹配。然而,這是以差分信號的共模噪聲抑制為代價的,后者的作用是使時鐘抖動保持在最小限度。

同樣重要的是,我們需要指出,密集的同相信號(偶數(shù)模式)會增大?eff,從而導致τpd變長。當單端信號的多個副本密集走線時,結(jié)果就會發(fā)生這種情況。

表3. 相鄰走線與隔離走線

圖2. 相鄰走線與隔離走線。

延遲匹配與頻率的關(guān)系

建議: 為了最大限度地減少頻率相關(guān)延遲匹配誤差,請選擇低Dk、低損耗因子(DF)的材料(Dk <3.7, DF <0.005)。DF也稱為損耗角正切(tan δ)(見等式6)。對于多GHz走線,請避免使用含鎳的電鍍技術(shù)。

通過抵消變化量,將不同頻率將信號之間的延時匹配到ps水平并非易事。圖3顯示隨著頻率的增加,介電常數(shù)通常會降低?;谏厦娴牡仁?和等式2,隨著頻率的增加,這種行為產(chǎn)生的τpd會變小?;诘仁?和圖3中的Roger材料,1 在10厘米走線上,1 GHz與20 GHz正弦波之間的Δτpd約為4 ps。

圖3同時顯示,信號衰減隨著頻率的增加而增加,與基音相比,導致方波高階諧波衰減增大。這種濾波的程度會導致上升時間(τR)和下降時間(τF)的不同。上升時間和下降時間的變化會表現(xiàn)在波形上的變化影響后繼接受器件,從而體現(xiàn)在總的時延參數(shù)上,總延遲由走線的τpd和信號的τR/2或τF/2構(gòu)成。另外,不同頻率的方波也可能具有不同的群延遲。由于這些原因,在估計不同頻率之間的延遲匹配時,方波比正弦波更具挑戰(zhàn)性。

為了更好地理解衰減(以dB/ft為單位的α)與頻率的關(guān)系,請參考等式7和等式8以及本文中提供的參考資料2,3,4,5,其中引入了損耗角正切(δ)和集膚效應。這些參考文獻的一個關(guān)鍵點是集膚效應減小了等式8中的面積(A),結(jié)果增大了線路電阻(R)。3 為避免高頻集膚效應引起過度衰減,請不要使用鍍鎳技術(shù),例如鍍金焊料掩模(SMOG)電鍍技術(shù)和化學鍍鎳浸金(ENIG)電鍍技術(shù)。4,5 避免使用鎳的電鍍技術(shù)的一個例子是裸銅焊料掩模(SMOBC)技術(shù)??偠灾?,選擇低Dk/DF的材料,避免使用鎳的電鍍技術(shù),并在關(guān)鍵走線上進行電路板級延遲仿真,從而改善不同頻率的延遲匹配。

圖3. Dk和DF與頻率的關(guān)系。

延遲匹配與溫度的關(guān)系

建議: 為PCB和電纜選擇溫度穩(wěn)定的介電材料。溫度穩(wěn)定型介電材料的Δ?ppm通常小于50 ppm。

介電常數(shù)隨溫度變化,導致傳輸線τpd的變化。等式4計算由于溫度變化導致的介電常數(shù)變化從而引起的時延的變化Δτpd。

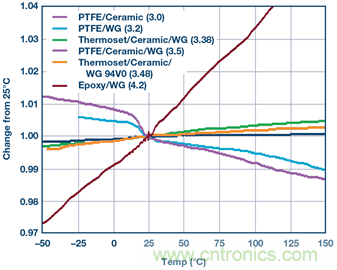

通常,PCB材料分為兩類:玻璃纖維織物(WG)和無紡玻璃。由于玻璃的Dk = 6,因此玻璃纖維通常更便宜并且Dk更高。圖4比較了各種不同材料的Dk變化。圖4顯示,一些基于PTFE/WG的材料在10°C和25°C之間的TCDk比較陡峭。

使用等式3和圖4,表4計算出了不同PCB材料上10厘米帶狀線走線在溫度于25°C至0°C之間變化時的Δτpd。在需要在不同溫度下跨多條走線匹配τpd的系統(tǒng)中,PCB材料的選擇可能在10厘米走線之間導致幾皮秒的τpd失配。

同軸電纜介電材料也有類似的TCDk問題。同軸電纜通常比PCB走線長得多,這將在整個溫度范圍導致大得多的Δτpd。當溫度從25°C變?yōu)?°C時,使用與表4第2列所示屬性相同的兩根1米電纜可能會產(chǎn)生25 ps的τpd失配。

表4假設走線長度為10厘米時,溫度恒定不變。在實際情況中,溫度在整條走線或同軸電纜上可能并不恒定,使得分析比上面討論的情況要復雜一些。

圖4. Dk變化與溫度的關(guān)系。

表4. 10厘米帶狀線的Δτpd,25°C至0°C

延遲匹配電纜

建議: 了解購買延遲匹配電纜與開發(fā)校準程序以通過電子方式調(diào)整延遲失配這兩種方式之間的成本權(quán)衡關(guān)系。

根據(jù)筆者的經(jīng)驗,比較同一供應商提供的相同長度和材料的同軸電纜,可以發(fā)現(xiàn)延遲失配在5 ps至30 ps之間。從與電纜供應商的討論來看,這一變化范圍是電纜切割、SMA安裝和Dk批次之間變化的結(jié)果。

許多同軸電纜制造商在提供相位匹配電纜,其預定匹配延遲窗口為1 ps、2 ps或3 ps。隨著延遲匹配精度的增加,電纜的價格通常也會增加。為了制造延遲匹配<3 ps的電纜,制造商通常會在電纜制造過程中增加若干延遲測量和電纜切割步驟。對于電纜制造商而言,這些增加的步驟會導致制造成本增加并降低產(chǎn)量。

延遲匹配與電纜彎曲

建議:在選擇電纜材料時,要了解由于溫度引起的延遲偏移與電纜彎曲引起的延遲偏移之間的權(quán)衡關(guān)系。

彎曲同軸電纜會導致不同的信號延遲。電纜供應商的數(shù)據(jù)手冊通常會規(guī)定特定彎曲半徑和頻率下彎曲90°時的相位誤差。例如,在頻率為18GHz、彎曲角度為90°時,額定相位變化可能為8°。使用等式5,計算得到的延遲大約為1.2 ps。

延遲匹配與SMA的安裝和選擇

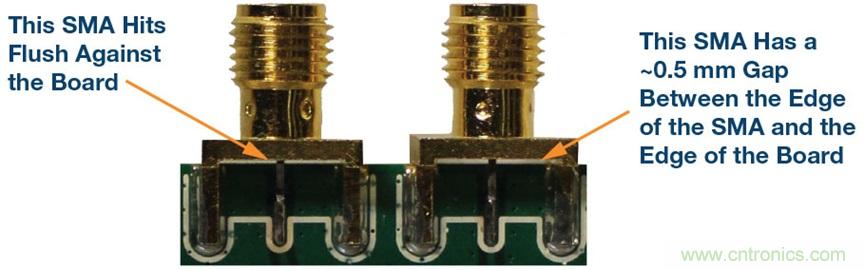

PCB邊緣安裝SMA在安裝時的變化會增加時鐘路徑之間的延遲失配,如圖5所示。通常不會測量這種性質(zhì)的誤差,因此很難量化。但是,我們可以合理地假設,這可能會在時鐘路徑之間增加1 ps至3 ps的延遲失配。

圖5. SMA安裝延遲失配。

控制SMA安裝引起的延遲失配的一種方法是選擇具有對齊特性的SMA,如圖6所示。由于具有對準特性的SMA的額定頻率通常高于沒有對準特性的SMA,因此成本更高,二者之間存在折衷。SMA供應商經(jīng)常為更高頻率的SMA提供推薦的PCB到SMA發(fā)射板布局。該推薦的布局本身就有可能值得付出額外的代價,因為這樣就可以節(jié)省電路板修訂成本,當時鐘頻率大于5 GHz時,尤其如此。

圖6. 具有對齊特性的SMA。

跨多個PCB的延遲匹配

建議: 了解購買批次間?r控制良好的PCB材料與開發(fā)校準程序以 通過電子方式調(diào)整延遲失配這兩種方式之間的成本權(quán)衡關(guān)系。

試圖在多塊PCB上的走線之間匹配τpd會增加若干誤差源。上面討論了四個誤差源:延遲匹配與溫度;延遲匹配電纜;延遲匹配與電纜彎曲;以及延遲匹配與SMA的安裝和選擇。第五個誤差源是?r在多個PCB上因工藝導致的變化。聯(lián)系PCB制造商,以了解?r的工藝變化。

作為一個例子,F(xiàn)R-4的?r可能在4.35到4.8之間變化。6 對于不同PCB上10厘米長的帶狀線走線,在極端情況下,該范圍會產(chǎn)生高達35 ps的Δτpd。其他PCB的材料數(shù)據(jù)手冊提供的?r典型范圍更小。例如,Rogers 4003C的數(shù)據(jù)手冊稱,其?r的范圍為3.38 ± 0.05。對于不同PCB上的10厘米帶狀線走線,在極端情況下,該范圍會將可能的Δτpd降至9 ps。

時間IC導致的相位偏差

建議: 考慮偏差調(diào)整幅度<1 ps的新型PLL/VCO IC。

過去,數(shù)據(jù)轉(zhuǎn)換器時鐘是從多個輸出時鐘器件生成的。這些時鐘器件的數(shù)據(jù)手冊規(guī)定了器件的相位偏差,范圍通常為5 ps至50 ps,具體取決于所選的IC。據(jù)筆者所知,在擬定本文時市場上的所有多輸出GHz時鐘IC都不具備對每個輸出調(diào)整時鐘延遲的能力。

隨著大于6 GHz的數(shù)據(jù)轉(zhuǎn)換器時鐘頻率不斷普及,單輸出或雙輸出PLL/VCO將成為首選時鐘。單輸出PLL/VCO時鐘IC架構(gòu)的優(yōu)勢在于,人們正在開發(fā)一些方法,以便以<1 ps的步長調(diào)整參考輸入到時鐘輸出的延遲。對每個時鐘調(diào)整參考輸入到輸出的延遲,這種能力允許最終用戶執(zhí)行系統(tǒng)級校準,將相位偏差最小化到1 ps以下。這種系統(tǒng)級相位偏差校準有可能降低本文中緩解的所有PCB、電纜和連接器延遲匹配問題,從而降低系統(tǒng)的整體BOM成本。

結(jié)論

本文討論了可能延遲變化和延遲失配的幾種來源。討論表明,?eff可能隨溫度、頻率、工藝、傳輸線類型和線路間距而變化。同時表明,通過同軸電纜連接的多PCB設備會產(chǎn)生額外的延遲變化源。當選擇材料以最小化大時鐘樹的相位偏差時,我們必須了解PCB和電纜?r隨溫度、工藝和頻率而變化的規(guī)律。對于所有這些變量,如果沒有某種偏差校準,很難設計出偏差<10 ps的大時鐘系統(tǒng)。此外,購買PCB材料、同軸電纜和SMA連接器以最大限度地減少相位偏差會顯著增加材料成本。為簡化校準方法并降低系統(tǒng)成本,IC制造商提供的許多新型PLL/VCO和時鐘器件可實現(xiàn)低于1 ps的延遲調(diào)整能力。

表5總結(jié)了本文針對最小化相位偏差而討論的建議。

表5. 關(guān)于最小化相位偏差的建議小結(jié)(按主題分)