【導讀】聚焦于PCIe 3.0和4.0中的動態(tài)均衡技術,本文介紹其原理、實現(xiàn)及其相關的一致性測試,這種動態(tài)均衡技術被稱作“Link Equalization”(鏈路均衡,簡稱為LEQ)。本系列文章分上下兩篇,本文是下篇實踐篇,重點介紹Rx鏈路均衡的測試和調試,泰克公司的自動化軟件為此提供了業(yè)界最優(yōu)的解決方案。

聚焦于PCIe 3.0和4.0中的動態(tài)均衡技術,本文介紹其原理、實現(xiàn)及其相關的一致性測試,這種動態(tài)均衡技術被稱作“Link Equalization”(鏈路均衡,簡稱為LEQ)。本系列文章分上下兩篇,本文是下篇實踐篇,重點介紹Rx鏈路均衡的測試和調試,泰克公司的自動化軟件為此提供了業(yè)界最優(yōu)的解決方案。

另外,泰克PCI Express專家David Bouse將在4月10日(周五)13:00-16:00直播課堂【PCI Express 5.0規(guī)范更新解讀和測試揭秘】講解如何解決PCIe 5.0的新測試挑戰(zhàn)https://info.tek.com/cn-pcie-mofu.html。

接收端鏈路均衡測試(Rx LEQ)

在PCIe 2.0的時代,通常只要保證了發(fā)送端的信號質量,那么整個系統(tǒng)也就能夠正常工作;因此接收端測試并不是必測項。但在PCIe 3.0/4.0中,由于速率成倍的增加;并且又經(jīng)過長走線的傳輸,因此在接收端采用了復雜的均衡技術;因此在PCIe 3.0/4.0中接收端測試屬于必測項。

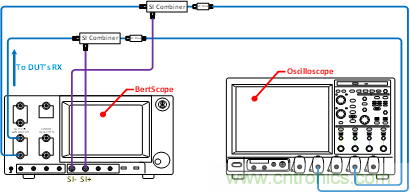

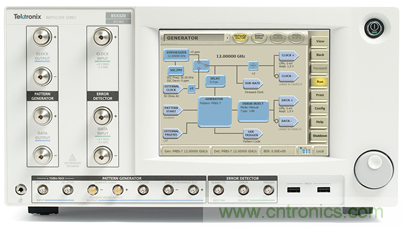

泰克公司的BSX系列的誤碼儀是業(yè)界高性能的串行誤碼儀,能夠實現(xiàn)高達32Gbps的碼型發(fā)生和誤碼分析功能,同時其內部集成有預加重模塊、噪聲注入、抖動注入等,支持基于協(xié)議的握手功能。因此非常適合PCIe 3.0和4.0的接收端測試。由于BSX系列最高支持到32Gbps,因此它也可以充分地滿足未來的PCIe 5.0的接收端測試的要求。圖1是使用BSX系列的誤碼儀進行PCIe 3.0d的接收端測試的示意圖。

圖1 PCIe 3.0的接收端測試的示意圖

在PCIe 3.0 & 4.0的接收端內部集成了復雜的單元,例如:均衡電路、時鐘恢復電路、以及判決電路等;它們都是不能直接探測到的。因此,接收端對于測試人員來說,是一個黑盒子。PCI-SIG協(xié)會的規(guī)范開發(fā)人員,在面臨此種困難時,開發(fā)了一套被稱作“壓力眼圖(Stressed Eye)”的方法論來完成對接收端的評估。這種方法論的核心思想就是:通過向接收端施加一個嚴重劣化的信號(即壓力眼圖),來檢測在此種情況下,接收端是否仍能夠正確地接收信號。因此,無論是PCIe 3.0 & 4.0 Rx LEQ的測試,基本上都可以分解成三個步驟:壓力眼圖的校準、進入環(huán)回模式、進行誤碼率測試。

壓力眼圖的校準就是:定量地規(guī)定這個劣化信號劣化到何種程度、以及測量該劣化信號的方法;

進入環(huán)回模式:為了檢測接收端是否正確接收該信號;需要將已經(jīng)接收到的信號原封不動地環(huán)回到待測的發(fā)送端;然后誤碼儀對這個環(huán)回的信號進行判斷。因此需要讓待測進入環(huán)回模式;

進行誤碼率測試:使用規(guī)定好的碼型進行誤碼率測試。

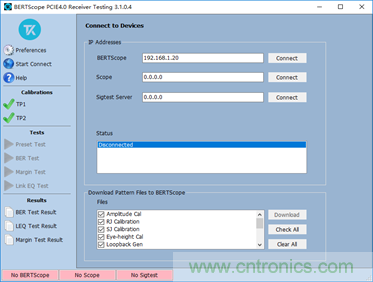

在壓力眼圖的校準時,涉及到信號的特性分析以及調整迭代,這些都需要反復進行,人工手動操作非常地耗時,并且吃力不討好。為此,泰克公司提供了業(yè)界最優(yōu)的PCIe Rx自動化測試軟件(BSXPCI4CEM),如圖2所示。通過泰克公司的PCIe Rx自動化測試軟件,可以大大縮短開發(fā)人員的研發(fā)時間,提供產(chǎn)品的可靠性。

圖2 泰克PCIe Rx自動化軟件GUI界面

對于這個壓力眼圖惡劣到何種程度,必須要進行精確地定量地描述,因此在PCIe的規(guī)范中,給出了這個壓力眼圖的要求。無論是PCIe 3.0還是PCIe 4.0,校準過程都分為兩個階段:

? TP1校準:TP1指的是整個參考信道的近端,在該處校準幅度、隨機抖動Rj、正弦抖動Sj、以及Tx EQ。

? TP2校準:TP2指的是整個參考信道的遠端,在該處校準DMSI、CMSI、以及最終的眼高/眼寬。

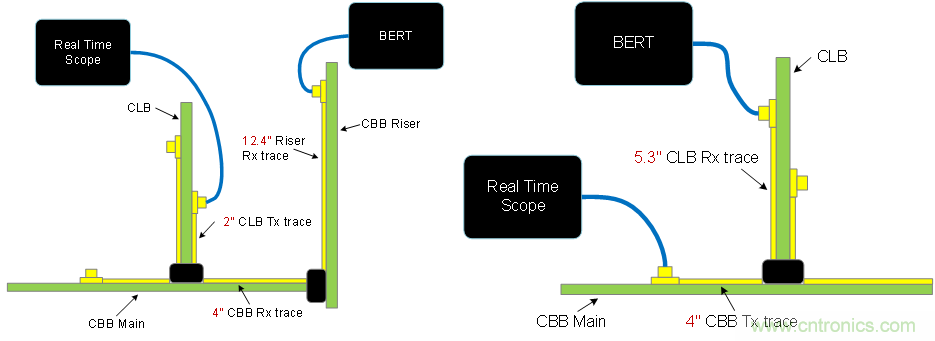

無論是PCIe 3.0,還是PCIe 4.0,TP1的校準過程都是一樣的,而且較為簡單;不區(qū)分待測對象是插卡還是系統(tǒng)板,整個拓撲連接如圖3所示。

圖3 PCIe 3.0 & 4.0的TP1校準拓撲連接

TP2校準則連接較為復雜,耗時較長;并且對于插卡和系統(tǒng)板來說,拓撲連接是不同的。而且在PCIe 3.0和PCIe 4.0中,TP2校準的策略有所不同。在PCIe 3.0中,是通過調整DMSI和Rj來達到最終的眼高/眼寬。而在PCIe 4.0中,則主要通過調整ISI來使得眼圖接近最終的眼高/眼寬,這一過程為粗調;然后再通過調整Sj、DMSI、或幅度來獲得最終的眼圖,這一過程為細調。

PCIe 3.0的TP2校準的拓撲連接如圖4所示。對于插卡的校準來說,在其拓撲連接中采用的是兩連接頭的拓撲結構,這是為了模擬真實的服務器背板的惡劣信道情況。整個參考信道是由圖4(a)中的物理參考信道和SigTest通過軟件嵌入的信道兩部分組成。

(a) (b)

圖4 PCIe 3.0 TP2校準拓撲連接:(a) 插卡的校準 (b) 系統(tǒng)板的校準

完成了拓撲連接之后,就可以進行PCIe 3.0的TP2的校準了。在最終眼高/眼寬的校準過程,通過調整Rj和DMSI,來達到最終的眼高/眼寬要求。這里存在的風險是:有時候協(xié)會提供的治具一致性較差;需要很大的Rj或DMSI才能夠達到最終的眼高/眼寬要求。而這并不符合在真實的情況下的Rj和DMSI的情況。

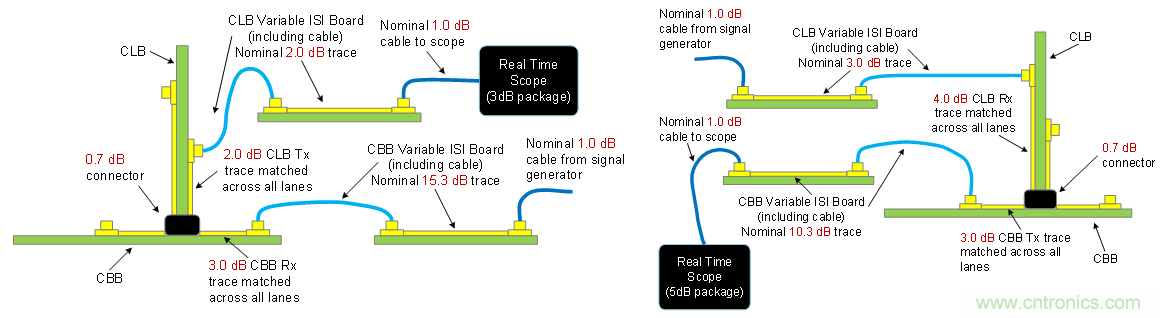

因此在PCIe 4.0中TP2的校準修改了相應的校準策略,引入了一個ISI板,優(yōu)先來調節(jié)參考信道的ISI值,來對眼圖進行調整。當眼圖接近到最終的眼高/眼寬附近時,再通過調整DMSI,Sj和幅度來達到最終的眼高/眼寬,并且DMSI,Sj和幅度的調整范圍做了限制,從而能夠比較真實地模擬現(xiàn)實中的情況。

PCIe 4.0的TP2校準的拓撲連接如圖5所示。與PCIe 3.0相比,除了參考信道的末端嵌入了一個封裝損耗之外,其他的信道都是由真實的物理信道組成的。并且由于速率翻倍,在拓撲連接中,鏈路損耗的估算時必須要將連接線纜等的損耗計入在內。值得注意的是:封裝損耗是在示波器之中嵌入的,而不是在SigTest中。這個參考封裝損耗是為了模擬真實情況下的芯片封裝損耗,由于RC芯片(Root Complex)的封裝一般比EP芯片(Endpoint)的封裝要大,因此針對RC的參考封裝損耗為5dB;而針對EP的參考封裝損耗為3dB。

(a) (b)

圖5 PCIe 4.0 TP2校準拓撲連接:(a) 插卡的校準 (b) 系統(tǒng)板的校準

如前所述,在PCIe 4.0的校準過程中,需要參考信道的ISI值,這就涉及到一個ISI pair的迭代過程,整個迭代過程的起點是-28 dB的端到端的損耗,依據(jù)計算出來的眼高/眼寬來確定下一個ISI pair;端到端的損耗調整范圍為-27 dB ~ 30dB。泰克公司的PCIe Rx自動化軟件能夠提供鏈路端到端損耗的估算,用戶可以自行決定是否繼續(xù)進行ISI迭代。

進入環(huán)回模式

LEQ的測試對測試儀器提出了很高的要求。它要求測試儀器能夠完成協(xié)議級別的動態(tài)應答和訓練。在工業(yè)界中,一般稱這樣的儀器為“協(xié)議感知”型儀器(Protocol-aware Instrument)。

泰克公司的BSX系列誤碼儀就是這樣的一種協(xié)議感知型儀器,支持的速率最高可到32Gbps;可以支持多種標準協(xié)議,例如PCIe 3.0 & 4.0 & 5.0、USB 3.1 & 3.2等。另外,用戶還可以通過自帶的Pattern Sequencer功能完成各種自主開發(fā)的標準的測試。

圖6 泰克公司的協(xié)議感知型誤碼儀:BSX系列

對于PCIe 3.0 & 4.0來說,從狀態(tài)機的角度,有兩種方式進入環(huán)回模式,如圖7所示:

(a) (b)

圖 7 PCIe 3.0&4.0進入環(huán)回模式:(a)從Configuration進入 (b)從Recovery進入

進行誤碼率測試

若成功了進入了Loopback,那么后續(xù)的誤碼率測試就很簡單。誤碼儀發(fā)送Modified Compliance Pattern,檢查1012個比特數(shù)據(jù);若不超過1個誤碼;那么就算通過;否則就未通過。

診斷和調試

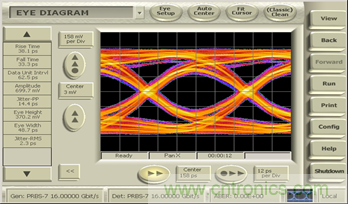

在實際的Rx LEQ的測試中,經(jīng)常由于種種原因,無法進入到環(huán)回模式;或者就算進入到了環(huán)回模式,也存在較多的誤碼。這個時候,我們就需要超出一致性測試;而進行一系列的調試工作,來找出根因(Root Cause)。

圖8 使用誤碼儀的眼圖功能觀測待測對象的環(huán)回數(shù)據(jù)輸出的信號質量

泰克公司PCIe Rx自動化測試軟件,除了提供協(xié)會所要求的一致性測試之外,還提供了豐富的調試功能。再配合上BSX系列的誤碼儀的通用調試功能,能夠為用戶提供全方位的靈活性。

在進行Rx LEQ環(huán)回測試時,有兩條數(shù)據(jù)通路:接收數(shù)據(jù)通路和環(huán)回數(shù)據(jù)通路。由于Rx LEQ是針對接收數(shù)據(jù)通路的測試,因此用戶必須保證不會由于環(huán)回數(shù)據(jù)通路的原因而導致誤碼儀的DET進行了誤判。泰克的BSX系列的誤碼儀具有豐富的眼圖測試功能,如圖8所示。這樣用戶再不進行任何拓撲連接改變的情況下,就能夠進行誤碼的調試。

用戶可以使用泰克公司提供的“Empty A – Modified Compliance B.ram”文件,就能夠使得被測對象穩(wěn)定地進入Compliance模式,然后通過這個ran文件進行碼型切換,將被測對象的輸出端切換到8Gbps或16Gbps,觀察哪個預設定值能夠給出最好的眼圖。然后在圖9中設置“Preset/Hint”成剛才的預設置,就能夠保證環(huán)回數(shù)據(jù)通路不會引入誤判的誤碼。

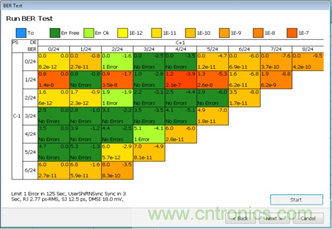

倘若排除了環(huán)回數(shù)據(jù)通路所引入的誤判的誤碼;Rx LEQ仍然存在誤碼。這個時候,用戶需要進一步分析誤碼的來源,比如說是否是DUT的均衡算法沒有達到最優(yōu),從而沒有像鏈路對端請求最優(yōu)的Tx EQ值。此時,用戶可以使用泰克公司提供的“BER Test”來對整個系數(shù)空間進行掃描,若測得的結果表明:在系數(shù)空間中存在一些系數(shù)組合能夠達到?jīng)]有誤碼,那么說明DUT的均衡算法未達到最優(yōu)。

圖9 對Tx EQ的系數(shù)空間進行掃描的誤碼率測試

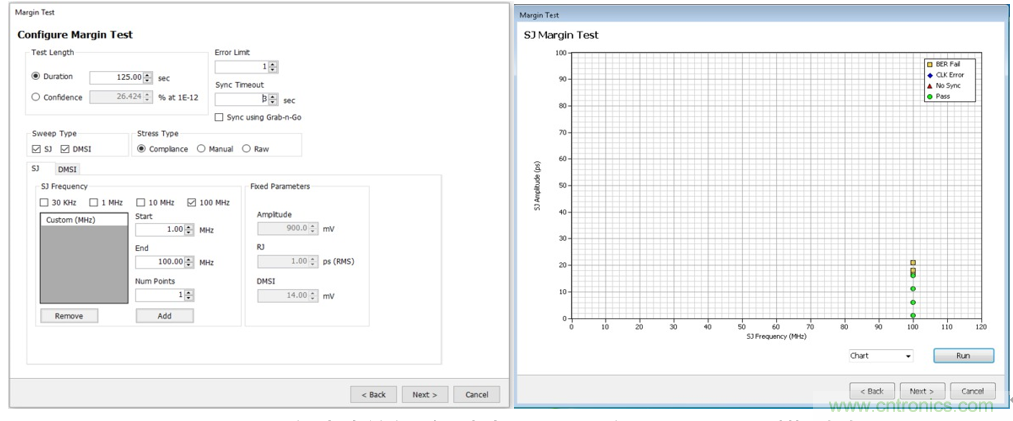

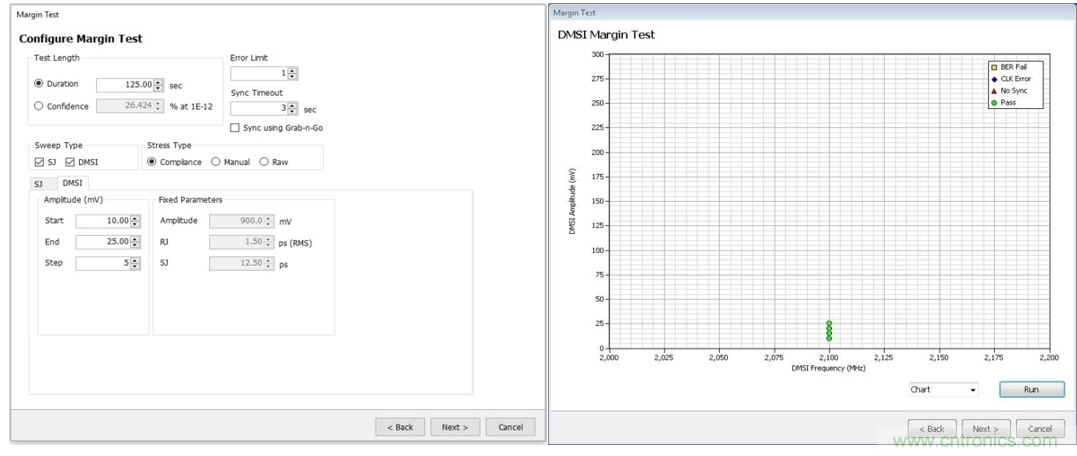

在此基礎上還可以進行裕度測試。泰克的自動化軟件提供對Sj和DMSI的裕度測試,如圖10、11所示。

圖 10 正弦抖動的裕度測試:(a) 設定界面 (b) 掃描測試界面

圖 11 差模噪聲的裕度測試:(a) 設定界面 (b) 掃描測試界面

泰克公司提供了業(yè)界領先的關于PCIe 3.0 & 4.0的一致性解決方案,通過使用泰克公司的高性能的示波器、高性能的誤碼儀、以及靈活的自動化軟件,能夠大大縮短用戶的開發(fā)時間,使得用戶的產(chǎn)品在市場上更具競爭力。

關于泰克科技

泰克公司總部位于美國俄勒岡州畢佛頓市,致力提供創(chuàng)新、精確、操作簡便的測試、測量和監(jiān)測解決方案,解決各種問題,釋放洞察力,推動創(chuàng)新能力。70多年來,泰克一直走在數(shù)字時代前沿。

(來源:泰克科技應用工程師,作者:李煜)

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯(lián)系小編進行處理。