【導讀】為了提供更多的功能,芯片變得越來越大,但是相反,封裝卻被要求以更小的尺寸來容納這些更大尺寸的裸片。這就不可避免地要求,新的候選封裝技術既能提高系統(tǒng)效率又能降低制造成本。

為了提供更多的功能,芯片變得越來越大,但是相反,封裝卻被要求以更小的尺寸來容納這些更大尺寸的裸片。這就不可避免地要求,新的候選封裝技術既能提高系統(tǒng)效率又能降低制造成本。

封裝創(chuàng)新涉及的領域包括更廣泛的額定電流和額定電壓、散熱及故障保護機制等。本文列出了工程師在為半導體器件評估封裝技術特性時需要考慮的關鍵因素。

我們從最通常的疑惑開始:小型的封裝尺寸。

1. 更小的封裝尺寸

現(xiàn)在,我們希望IC封裝能夠節(jié)省電路板空間,幫助實現(xiàn)更堅固的設計,并通過省去一些外部元器件來降低PCB的組裝成本。因此,業(yè)界正在對諸如D2PAK 7的IC封裝技術進行優(yōu)化,以期以相同的尺寸和引出線容納面積增加高達20%的裸片。

新的封裝設計還提供了可互換引出線選擇,從而最大限度地利用尺寸,并提供更大的設計靈活性。然后是直插或曲插引腳式封裝,這有助于優(yōu)化電路板空間和所需的引腳分離。

業(yè)界也正在開發(fā)一些閾值電壓在邏輯電平、面向電池供電設計的新封裝,這樣的封裝使微控制器可以直接驅動諸如MOSFET的功率器件。此舉也相應節(jié)省了電路板空間。

2. 功率密度

電機驅動器、太陽能逆變器和電源等等產品對功率芯片和模塊的需求在不斷增長,這拉動了在不增加封裝尺寸的條件下對更高功率密度的需求。

設計師如何在保持封裝魯棒性和可靠性的同時,提高功率密度?首先,封裝可以采用更大的引線框架面積,從而可以容納諸如IGBT的更大的功率芯片。這也實現(xiàn)了較低的封裝熱阻,而有利于改善散熱。

以意法半導體(ST)的新系統(tǒng)級封裝(SiP)PWD13F60為例,它將4個功率MOSFET集成在了比同類電路小60%的封裝內(圖1)。PWD13F60封裝集成了面向功率MOSFET的柵極驅動器、面向上側驅動的自舉二極管、交叉?zhèn)鲗ПWo和欠壓鎖定。

圖1:意法半導體的SiP解決方案,面向工業(yè)電機驅動器、燈鎮(zhèn)流器、電源、轉換器和逆變器應用。

關斷電路可保護功率開關,欠壓鎖定可防止低壓故障。同樣,自舉二極管可減少物料清單(BOM),簡化電路板布局。

它表明了封裝選擇對于最大限度地提高能效和適應廣泛的供電電壓范圍為何至關重要。在此,還值得指出的是,封裝的功率密度與散熱條件的改善相輔相成。

3. 散熱效率

由于像IGBT這樣的器件工作在較低溫度可減小器件上的應力,因此封裝的散熱性能與其可靠性存在內在聯(lián)系(圖2)。由于溫度較低所需的散熱器尺寸就不大,因此散熱特性也會影響散熱器大小。此外,冷卻要求的降低也為設計者在增加功率密度方面留有更大余地。

圖2:英飛凌的功率模塊封裝采用了熱接口材料(TIM)。

有些封裝保留了封裝的尺寸和高散熱效率的底部設計,同時將頂部源極裸露作為散熱區(qū)。此舉可實現(xiàn)更高的額定電流值,從而實現(xiàn)更高的功率密度和更小的封裝尺寸。

4. 散熱

用于在封裝內部產生隔離的常規(guī)方法通常既昂貴又難以處理。而且,它們遠不足以管理IGBT等高功率密度器件的散熱。

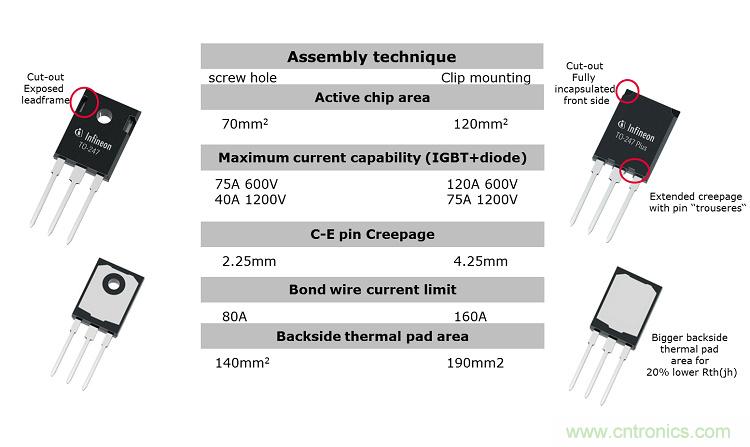

因此,英飛凌推出了一種叫做Trenchstop高級隔離的封裝技術(圖3)。這家德國芯片廠家稱,Trenchstop封裝技術可以取代全隔離封裝(FullPAK)以及標準隔離箔。英飛凌將這種新封裝定位于面向空調的功率因數(shù)校正(PFC)、不間斷電源(UPS)和電源轉換器等應用。

圖3:右側封裝的發(fā)熱量減少了15%。(圖片來源:英飛凌科技)

這種隔離封裝不再需要隔離材料和導熱硅脂,從而使設計人員能將裝配時間縮短高達35%。同時,因為不存在隔離箔未對齊的情況,所以它還提高了可靠性。這也實現(xiàn)了比FullPAK工作溫度低10℃的改進。

5. 開關損耗

特別是對像工業(yè)驅動器等器件中工作頻率高達20kHz的硬開關電路,為提高封裝效率,減少開關損耗勢在必行。此外,可靠的開關和低EMI增強了小功率應用中的無散熱器工作。

為降低開關損耗,一些封裝解決方案采用了額外的開爾文發(fā)射極電源引腳(圖4)。它旁路了柵極控制回路的發(fā)射極引線電感,從而提高了器件的開關速度,降低了開關能量。

圖4:具有開爾文發(fā)射極的封裝可將動態(tài)損耗降低20%。(圖片來源:英飛凌科技)

本文轉載自EDN電子技術設計。

推薦閱讀: