【導(dǎo)讀】系統(tǒng)設(shè)計(jì)師面對(duì)邏輯器件的多元化及苛刻的電源要求,要想設(shè)計(jì)出滿足電源需求的電源系統(tǒng)也變得越發(fā)艱難。那有什么好的方法來(lái)圓滿解決這種問(wèn)題呢?當(dāng)然!本文就論述了可編程電源系統(tǒng)的優(yōu)勢(shì)和收益,并且討論了眾多降低系統(tǒng)設(shè)計(jì)風(fēng)險(xiǎn)的方法。

由于當(dāng)前復(fù)雜邏輯器件的多元化及不斷變化的電源要求,對(duì)于系統(tǒng)設(shè)計(jì)師來(lái)說(shuō),開(kāi)發(fā)能夠滿足系統(tǒng)電源需求的電源系統(tǒng)也變得越發(fā)艱難。開(kāi)發(fā)期間及開(kāi)發(fā)之后,與電源電壓的調(diào)整需求相比,固定電壓電源系統(tǒng)的靈活性差,這會(huì)增大設(shè)計(jì)風(fēng)險(xiǎn),導(dǎo)致設(shè)計(jì)項(xiàng)目延遲甚至被取消。而可編程電源系統(tǒng)能夠滿足這種靈活性的需求,從而圓滿地解決這一問(wèn)題。本文論述了可編程電源系統(tǒng)的優(yōu)勢(shì)和收益,并且討論了眾多降低系統(tǒng)設(shè)計(jì)風(fēng)險(xiǎn)的方法。

多年前,系統(tǒng)設(shè)計(jì)師在設(shè)計(jì)系統(tǒng)電源時(shí)相對(duì)容易一些。邏輯運(yùn)行需要5V電源,硬盤(pán)和軟盤(pán)驅(qū)動(dòng)器需要 12V電源;系統(tǒng)其他器件采用雙電源電壓來(lái)運(yùn)行,或者可以添加一個(gè)負(fù)電壓電源。指定三種電源。易用性。

如今的復(fù)雜邏輯器件(FPGA、ASIC、SoC、ASSP等)有著更為復(fù)雜的電源要求。系統(tǒng)中一個(gè)芯片便有可能需要三種或四種電源電壓。更糟糕的是,多個(gè)電源電壓的啟動(dòng)順序和定時(shí)對(duì)系統(tǒng)初始化起著至關(guān)重要的作用。斷電操作期間切斷電壓的順序?qū)π酒恼MC(jī)同樣重要,并且還能夠極為有效地防止電源對(duì)IC造成的損壞。復(fù)位線或者多個(gè)復(fù)位線與電源電壓之間的定時(shí)關(guān)系也同樣相當(dāng)重要。

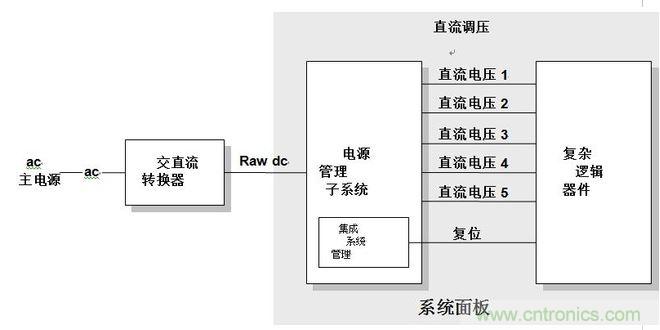

此外,電源系統(tǒng)必須與當(dāng)前的許多復(fù)雜系統(tǒng)實(shí)時(shí)交互,并且必須能夠根據(jù)快速波動(dòng)線和加載要求來(lái)實(shí)現(xiàn)實(shí)時(shí)重新配置。簡(jiǎn)而言之,與從前相比,當(dāng)今復(fù)雜數(shù)字系統(tǒng)的電源系統(tǒng)設(shè)計(jì)有著更為深遠(yuǎn)的考量,它促進(jìn)了電源管理系統(tǒng)的發(fā)展,與圖1所示一樣,這是為了滿足當(dāng)今越來(lái)越復(fù)雜的系統(tǒng)設(shè)計(jì)需求。然而,與以往相比,系統(tǒng)設(shè)計(jì)師卻較少考慮到這些問(wèn)題,這是由于他們更加關(guān)注極復(fù)雜邏輯系統(tǒng)的工作性能,以及大量相關(guān)固件是否能夠與硬件設(shè)計(jì)充分集成。

圖1,合并有電源管理系統(tǒng)的系統(tǒng)設(shè)計(jì)簡(jiǎn)化框圖。

電源問(wèn)題以及系統(tǒng)設(shè)計(jì)師的設(shè)計(jì)風(fēng)險(xiǎn)

系統(tǒng)設(shè)計(jì)師需要定制電源以便處理當(dāng)今 FPGA、介質(zhì)處理器、ASIC、SoC和 ASSP 的電源需求。在未來(lái),這一趨勢(shì)必然仍將持續(xù),但是有許多設(shè)計(jì)師缺乏設(shè)計(jì)高效率開(kāi)關(guān)電源所需的技能,也沒(méi)有時(shí)間去學(xué)習(xí)如何使用多個(gè)必要的傳統(tǒng)電源管理控制芯片來(lái)創(chuàng)建多電壓電源; 同時(shí)還缺乏進(jìn)行復(fù)雜計(jì)算的愿望,以及缺乏學(xué)習(xí)如何選擇不熟悉的電源元件如電源 FET和電源電感器的愿望。簡(jiǎn)而言之,系統(tǒng)設(shè)計(jì)師在開(kāi)發(fā)日益復(fù)雜的電源系統(tǒng)方面所花費(fèi)的時(shí)間越來(lái)越少。正由于所花的時(shí)間不夠,大大提高了設(shè)計(jì)電源時(shí)的風(fēng)險(xiǎn),導(dǎo)致電源不滿足要求,需要返工,因而延誤了產(chǎn)品的推出。

此外,系統(tǒng)設(shè)計(jì)師需要降低由于元件置換導(dǎo)致的設(shè)計(jì)要求變更風(fēng)險(xiǎn)、降低由芯片電源規(guī)范更改而產(chǎn)生的設(shè)計(jì)風(fēng)險(xiǎn),或者減少在整個(gè)電源電壓調(diào)整期間對(duì)芯片性能進(jìn)行微調(diào)的需求,所有上述風(fēng)險(xiǎn)系數(shù)都可通過(guò)利用可編程電源來(lái)緩和??删幊屉娫纯梢愿鶕?jù)當(dāng)前系統(tǒng)元件不斷變化的要求,或者根據(jù)由于元件置換或系統(tǒng)擴(kuò)充而產(chǎn)生的新要求來(lái)調(diào)整。有一種極為有效的方法可以處理生產(chǎn),下線前及生產(chǎn),下線后的元件變化。

因此,系統(tǒng)設(shè)計(jì)師需要找到能夠快便捷地開(kāi)發(fā)靈活插件板電源系統(tǒng)的新方法,該電源系統(tǒng)需能夠?qū)崿F(xiàn)運(yùn)行時(shí)的電源電壓重新編程,以處理未來(lái)在面對(duì)系統(tǒng)電源要求時(shí)的諸多未知難題。這種靈活且易于設(shè)計(jì)配置的電源系統(tǒng)可降低系統(tǒng)設(shè)計(jì)風(fēng)險(xiǎn)。同樣重要的是:這些可編程電源系統(tǒng)極大地增強(qiáng)了設(shè)計(jì)靈活性,從而降低了系統(tǒng)設(shè)計(jì)風(fēng)險(xiǎn),卻不會(huì)提高電源成本。

[page]

電源發(fā)展趨勢(shì)

隨著當(dāng)前系統(tǒng)復(fù)雜性越來(lái)越高,其對(duì)電源的要求也不斷增長(zhǎng),電源系統(tǒng)需要擁有比以往更高的能力應(yīng)對(duì)當(dāng)前的復(fù)雜系統(tǒng)。除了需要更多樣的電源電壓、電源、復(fù)位順序以及偏移不靈敏性之外,當(dāng)前的系統(tǒng)設(shè)計(jì)還需要對(duì)電源電壓進(jìn)行更為精密的可編程控制,如 FPGA、介質(zhì)處理器、SoC和 ASSP等高級(jí)芯片足以充分證明此點(diǎn),這些芯片是當(dāng)前系統(tǒng)的核心所在。例如,最高級(jí)的 FPGA 需要三種或四種電源電壓。

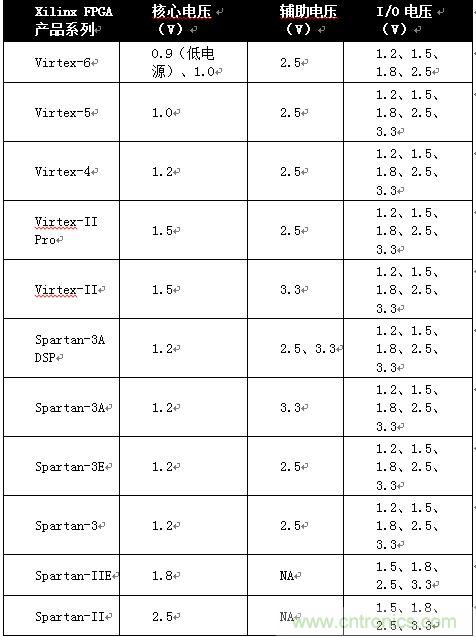

表1顯示了連續(xù)幾代 Xilinx Virtex和 Spartan FPGA所需的電源電壓。需注意的是,有些 FPGA需要兩種電源電壓,有些需要三種,全部三種電源電壓都可以假定每一代的電壓值均不相同,這取決于系統(tǒng)設(shè)計(jì)。

表1,Xilinx FPGA系列和各代產(chǎn)品的電源電壓。

其他 FPGA廠商(包括 Altera和 Lattice)對(duì)于電源的要求也呈現(xiàn)出相似性。表2顯示了 Altera的 FPGA產(chǎn)品系列擁有相似的電源電壓信息。

表2,Altera FPGA系列和各代產(chǎn)品的電源電壓。

表1和表2中所列的信息顯示了多種 FPGA電源電壓隨幾代元件的演變方式,因此與電源系統(tǒng)的討論息息相關(guān)。系統(tǒng)設(shè)計(jì)有可能需要適應(yīng)不同年代的FPGA或者采用不同核心電壓的不同產(chǎn)品系列的 FPGA。此外,這些相同的系統(tǒng)設(shè)計(jì)也有可能需要根據(jù)系統(tǒng)設(shè)計(jì)中的其他芯片而滿足不同的 I/O電壓要求。

[page]

需注意的是,表1并未對(duì) FPGA對(duì)電源系統(tǒng)所提出的要求做詳細(xì)說(shuō)明。所有 FPGA廠商均規(guī)定了確保 FPGA正常運(yùn)行所需的每一電源電壓的最小及最大必要?jiǎng)蜃儠r(shí)間(單位:微秒至毫秒)。在創(chuàng)建電源系統(tǒng)時(shí),這是系統(tǒng)設(shè)計(jì)師必須考慮的另一個(gè)因素。勻變時(shí)間不可過(guò)快或過(guò)慢。

對(duì)介質(zhì)處理器、SoC、ASSP和 ASIC的電源電壓有著類似的限制。由于對(duì)電源沒(méi)有標(biāo)準(zhǔn)規(guī)范,因此 IC設(shè)計(jì)小組可自由選擇完成設(shè)計(jì)所需的任何電源啟動(dòng)方案。滿足不斷變化的電源電壓要求是他人的問(wèn)題,而不由 IC設(shè)計(jì)小組負(fù)責(zé)。其他人通常指系統(tǒng)設(shè)計(jì)師。系統(tǒng)設(shè)計(jì)師負(fù)責(zé)滿足芯片的一切電壓和排序要求。當(dāng)一個(gè)系統(tǒng)設(shè)計(jì)中有多個(gè)復(fù)雜芯片時(shí),電源的復(fù)雜性便會(huì)翻倍。如需進(jìn)一步提高復(fù)雜性,可以將一個(gè)芯片的排序要求修訂為下一個(gè)序列,這樣便會(huì)需要更為準(zhǔn)確的器件特性或者會(huì)導(dǎo)致設(shè)計(jì)變更。此時(shí)仍然由系統(tǒng)設(shè)計(jì)師負(fù)責(zé)滿足這些需求,無(wú)論這些需求是什么,也無(wú)論這些需求如何變化。

鑒于這些原因,從根本上逐步提高系統(tǒng)復(fù)雜性以及系統(tǒng)中所用芯片的復(fù)雜性時(shí),需要將電源系統(tǒng)的能力改進(jìn)數(shù)倍,這就要求電源提供勻變倍數(shù),并且精確控制各種電源軌之間的定時(shí)關(guān)系。若欲實(shí)現(xiàn)電源系統(tǒng)的上述高級(jí)能力,通過(guò)采用早期電源管理設(shè)計(jì)方法成本巨大或者根本無(wú)法實(shí)現(xiàn)。

系統(tǒng)設(shè)計(jì)師電源簡(jiǎn)史

在查看創(chuàng)建可編程電源系統(tǒng)的潛在設(shè)計(jì)方法之前,我們來(lái)簡(jiǎn)要回顧一下早期的方法,以便理解如今的系統(tǒng)設(shè)計(jì)為什么有著更多需求。插件板上或負(fù)載點(diǎn)(POL)電源系統(tǒng)基于現(xiàn)有的開(kāi)關(guān)模式 PWM電源控制器和簡(jiǎn)單電源管理芯片。早期的開(kāi)關(guān)模式電源控制器采用易于理解的模擬 PID回路(比例,積分,微分回路)算法來(lái)調(diào)節(jié)電壓。這種設(shè)計(jì)表現(xiàn)良好但卻存在必須解決的設(shè)計(jì)問(wèn)題。

首先,這種控制器對(duì)外部元件隨時(shí)間和溫度的偏移非常敏感。這種偏移不會(huì)影響調(diào)節(jié)精度,因此根本不會(huì)影響電源控制器的調(diào)節(jié)能力。所有調(diào)節(jié)能力的潛在損失只與回路穩(wěn)定性有關(guān)。如果精心設(shè)計(jì)的補(bǔ)償回路中的控制器元件與設(shè)計(jì)規(guī)范的偏移足夠大,則控制回路會(huì)變得不穩(wěn)定,并且控制器也根本不再進(jìn)行調(diào)節(jié)。對(duì)這一問(wèn)題的解決方案是購(gòu)買(mǎi)對(duì)偏移敏感度較低的更昂貴外部元件,對(duì)于對(duì)成本較為敏感的設(shè)計(jì)來(lái)說(shuō),這一替代方式通常不建議采納。那么當(dāng)前,哪些設(shè)計(jì)對(duì)成本不敏感呢?

第二個(gè)問(wèn)題是系統(tǒng)兼容性。如之前所討論的那樣,有幾個(gè)與系統(tǒng)有關(guān)的問(wèn)題,包括電源排序、各種插件板上電源和復(fù)位信號(hào)或多個(gè)信號(hào)間的定時(shí)關(guān)系、對(duì)一個(gè)或多個(gè)插件板上電源進(jìn)線微調(diào)以實(shí)現(xiàn)系統(tǒng)正常操作的可能性。所有這些問(wèn)題都需要超越單一的 PWM控制器芯片能力。

因此,IC廠商創(chuàng)造了能夠充當(dāng)“數(shù)字包封”的電源管理芯片。這些芯片可控制多個(gè)模擬 PWM控制器的加電排序,可針對(duì)電源系統(tǒng)的設(shè)計(jì)來(lái)產(chǎn)生一個(gè)多芯片解決方案。盡管這一方法最初可以估算電源電壓排序和復(fù)位定時(shí)所需的靈活性類型,但由于電壓被與PWM控制器芯片有關(guān)的外部元件所固定,因此不能滿足用來(lái)調(diào)整系統(tǒng)電源電壓的各種生產(chǎn)前及生產(chǎn)后的需求。此外,向包含多個(gè) PWM控制器芯片的設(shè)計(jì)中添加電源管理芯片還會(huì)增添另一個(gè)芯片,這會(huì)提升成本、增大設(shè)計(jì)復(fù)雜性并且耗費(fèi)額外的面板空間。在看重設(shè)計(jì)空間尺寸的芯片中,這種電源系統(tǒng)設(shè)計(jì)解決方案會(huì)降低精密度。

現(xiàn)在我們需要什么?

我們現(xiàn)在需要的是一個(gè)可編程電源或者系統(tǒng)(PPS),它應(yīng)該能夠提供多種精細(xì)可編程電源電壓,并且在各個(gè)電源電壓之間提供可獨(dú)立調(diào)整的斜升和斜降時(shí)間以及可調(diào)的排序延時(shí)。這種電源系統(tǒng)設(shè)計(jì)為系統(tǒng)設(shè)計(jì)師提供了必要的設(shè)計(jì)靈活性。該系統(tǒng)如今未得到廣泛應(yīng)用的原因是其昂貴的價(jià)格。這種昂貴指的并不是基礎(chǔ)技術(shù)本身,而是由于電源 IC廠商以前未曾針對(duì)設(shè)計(jì)問(wèn)題采用充分的硅集成等級(jí)。但是,這種狀況注定會(huì)發(fā)生變化,而且這種變化已見(jiàn)端倪。

正如 FPGA可以方便地針對(duì)新系統(tǒng)需求或者不斷變化的系統(tǒng)需求為系統(tǒng)設(shè)計(jì)師提供靈活的可編程序邏輯結(jié)構(gòu)一樣, PPS也能夠?yàn)橄到y(tǒng)設(shè)計(jì)提供一種可編程電源系統(tǒng),以便匹配系統(tǒng)電源的所有變化或者新的要求。現(xiàn)場(chǎng)可編程性為這兩種情況賦予了極大的靈活性。對(duì)于 PPS來(lái)說(shuō),由于需要將硅集成從原有的 PWM技術(shù)完全轉(zhuǎn)換為數(shù)字控制電源系統(tǒng),因此靈活性的增強(qiáng)是免費(fèi)的。因此,系統(tǒng)設(shè)計(jì)師能夠顯著增強(qiáng)電源系統(tǒng)的特征而不會(huì)增加成本。

與以前開(kāi)發(fā)數(shù)個(gè)固定穩(wěn)壓器的方法相比,可編程電源系統(tǒng)能夠更加緊密地匹配當(dāng)前復(fù)雜系統(tǒng)的需求。與過(guò)去相比,由于復(fù)雜 IC的電源電壓達(dá)到了前所未有的穩(wěn)定性,因此如今的系統(tǒng)設(shè)計(jì)師對(duì)靈活性的要求更高。從前制作的 FPGA、微型控制器、SoC和 ASIC擁有穩(wěn)定的電源電壓規(guī)格,但是新零件,特別是仍處于α或β采樣階段的新零件,在下一次修訂時(shí)就有可能提出不同的要求。只有可編程電源系統(tǒng)能夠滿足這種情況下所需的靈活性。

此外,有可能需要由可編程電源系統(tǒng)通過(guò)調(diào)節(jié)元件的工作電壓來(lái)調(diào)整各種系統(tǒng)元件的運(yùn)行速度。當(dāng)工作電壓處于 1V時(shí),對(duì)電源電壓進(jìn)行“微調(diào)”會(huì)變得越來(lái)越普遍。

但即便在這種靈活性下,PPS的設(shè)計(jì)仍然比傳統(tǒng)開(kāi)關(guān)電源的設(shè)計(jì)更加簡(jiǎn)便。PPS器件采用基于軟件的設(shè)計(jì)工具來(lái)支持,這樣能夠更加簡(jiǎn)便地確定所需的電源電壓并且從設(shè)計(jì)工具中獲取所需的材料表(BOM)。此外,由于電源系統(tǒng)可編程,因此可以在電壓范圍內(nèi)調(diào)整電源系統(tǒng)的輸出,只需改動(dòng) PPS控制器的編程即可。對(duì)于某些 PPS控制器芯片來(lái)說(shuō),在系統(tǒng)操作期間,串行端口能夠讓插件板上的微型控制器來(lái)調(diào)整電源電壓。

PPS控制器還能夠?yàn)橄到y(tǒng)設(shè)計(jì)師帶來(lái)另一個(gè)實(shí)質(zhì)性的設(shè)計(jì)優(yōu)勢(shì):只需了解一個(gè)器件,便可掌握21世紀(jì)系統(tǒng)所需的所有電源電壓范圍。了解一個(gè)器件以及與該器件有關(guān)的一個(gè)軟件設(shè)計(jì)工具便能夠讓系統(tǒng)設(shè)計(jì)師掌握所有電源要求-初始要求、開(kāi)發(fā)要求以及操作要求-這樣能夠簡(jiǎn)化產(chǎn)品電源系統(tǒng)的設(shè)計(jì)。

為可編程電源控制器芯片提供 17種降低風(fēng)險(xiǎn)的方式

當(dāng)系統(tǒng)設(shè)計(jì)師在其設(shè)計(jì)中采用了各種不同的復(fù)雜邏輯器件時(shí),PPS控制器 IC能夠讓他們以更為簡(jiǎn)便的方式滿足電源需求。PPS控制器至少有 17種可以降低風(fēng)險(xiǎn)的具體方式:

(1)一個(gè) PPS控制器 IC可替換多個(gè)電源管理控制器,并且相關(guān)的系統(tǒng)設(shè)計(jì)有一個(gè)由集成電源系統(tǒng)管理器控制的可配置 PPS設(shè)計(jì),這簡(jiǎn)化了插件板上的電源管理以及負(fù)載點(diǎn)的電源電壓調(diào)節(jié),同時(shí)提高了整個(gè)可編程性范圍內(nèi)的電源可控性,以相同或者更低的BOM成本實(shí)現(xiàn)了更高的能力和更大的靈活性。

(2)PPS控制器 IC能夠顯著降低系統(tǒng)電源的元件數(shù)量,同時(shí)極大地?cái)U(kuò)展可控性。與基于模擬 PWM控制器的電源管理芯片相比,它能夠?qū)⒃O(shè)計(jì)電源時(shí)的插件板上無(wú)源器件數(shù)量減少至少 50%,甚至達(dá)80%,同時(shí)無(wú)需獨(dú)立排序和電源管理IC。

(3)基于 PPS控制器 IC的設(shè)計(jì)可降低整個(gè) FET驅(qū)動(dòng)器和系統(tǒng)管理集成的板面空間,并減少無(wú)源元件的數(shù)量。

(4)PPS控制器 IC的電源設(shè)計(jì)自適應(yīng)方式使得可編程電源基本上不受無(wú)源元件隨時(shí)間和溫度偏移的干擾,這樣就降低了電源設(shè)計(jì)對(duì)無(wú)源元件容差的敏感性,降低或者消除了組合面板的拷機(jī)需求。

(5)PPS 控制器 IC的自動(dòng)設(shè)計(jì)軟件能夠讓系統(tǒng)設(shè)計(jì)師利用簡(jiǎn)單而熟悉的基于 GUI的設(shè)計(jì)工具來(lái)快速設(shè)計(jì)完整功能的電源,而無(wú)需花費(fèi)時(shí)間去學(xué)習(xí)錯(cuò)綜復(fù)雜的數(shù)字PWM控制或電源管理,也無(wú)需進(jìn)行復(fù)雜卻易于出錯(cuò)的元件值計(jì)算(盡管工具能夠讓設(shè)計(jì)師隨心所欲地進(jìn)行眾多的詳細(xì)設(shè)計(jì))。自動(dòng)工具會(huì)即時(shí)創(chuàng)建 BOM。

(6)PPS控制器 IC的高集成度能夠讓設(shè)計(jì)師采用與FPGA相似的方式增添簡(jiǎn)單參數(shù)編程并重新配置所需的更為復(fù)雜的電源性能(電源排序、延時(shí)、勻變、電流限制以及電源電壓調(diào)整),而無(wú)需更改電源的硬件設(shè)計(jì)。

(7)PPS控制器 IC中的獨(dú)立可編程軟啟動(dòng)和軟停機(jī)電源參數(shù)降低了關(guān)鍵系統(tǒng)元件的開(kāi)通/關(guān)斷應(yīng)力。例如,當(dāng)系統(tǒng)經(jīng)由低等效串聯(lián)電阻(ESR)啟動(dòng)時(shí),不帶電的電源濾波器電容器會(huì)消耗數(shù)百安培的電流。軟啟動(dòng)電源會(huì)限制這些電流浪涌并且降低電纜、連接器和電容器本身承受的高電流應(yīng)力。軟關(guān)機(jī)能力可確保系統(tǒng)斷路時(shí),這些電容器充分放電。

(8)在整個(gè)編程過(guò)程中,PPS控制器 IC的可編程再配置性能夠?qū)⒆罱K的規(guī)范轉(zhuǎn)換為新型的復(fù)雜系統(tǒng)元件(FPGA、微型控制器、針對(duì)應(yīng)用程序的處理器)的電源要求,而無(wú)需對(duì)最終的面板等級(jí)、硬件設(shè)計(jì)進(jìn)行改動(dòng)。

(9)在整個(gè)器件的重新編程過(guò)程中,PPS控制器 IC的可編程再配置性能夠?qū)崿F(xiàn)復(fù)雜系統(tǒng)元件(FPGA、微型控制器、針對(duì)應(yīng)用裝置改編程序的處理器)的獨(dú)特而復(fù)雜的加電和斷電排序要求,而無(wú)需重新設(shè)計(jì)復(fù)雜的面板等級(jí)。

(10)PPS控制器 IC的可編程再配置性可以方便地滿足不斷變化的核心電源要求-例如有可能需要將FPGA更改為下一代 -只需進(jìn)行簡(jiǎn)單的配置編程變更,而無(wú)需進(jìn)行面板級(jí)設(shè)計(jì)更改或元件級(jí)BOM修正。

(11)PPS控制器 IC的可編程再配置性只需進(jìn)行簡(jiǎn)單的編程更改,便可方便地更改 I/O電源要求(例如有可能需要從 DDR更改為DDR2、低電源/低電壓DDR2或DDR3 SDRAM)。

(12)PPS控制器 IC配置參數(shù)的直接數(shù)字控制能夠讓系統(tǒng)主機(jī)、主電源或者輔助處理器來(lái)優(yōu)化主系統(tǒng)元件的運(yùn)行速度,只需稍稍改變系統(tǒng)中多個(gè)復(fù)雜邏輯器件的核心電源電壓即可。

[page]

(13)PPS控制器 IC的直接數(shù)字控制能夠讓系統(tǒng)主機(jī)、主電源或者輔助處理器管理工作電源級(jí)別以及由可編程斷電空轉(zhuǎn)系統(tǒng)元件或者系統(tǒng)的整個(gè)扇區(qū)所產(chǎn)生的熱量。

(14)PPS控制器 IC的直接數(shù)字控制通過(guò)對(duì)受影響的系統(tǒng)電源進(jìn)行排序,或者切斷失效且不重要的系統(tǒng),從而讓系統(tǒng)主機(jī)、主電源或者輔助處理器自動(dòng)管理插件板上與電源有關(guān)的假信號(hào)或者故障。

(15)PPS控制器 IC的直接數(shù)字控制提供了一條通信路徑,能夠遠(yuǎn)程修正或者更新所有電源電壓和加電/斷電順序,在系統(tǒng)就位后不會(huì)出現(xiàn)召回產(chǎn)品、服務(wù)請(qǐng)求或者上門(mén)服務(wù),這降低了系統(tǒng)的TCO(總擁有成本)。

(16)由于對(duì)關(guān)鍵系統(tǒng)元件進(jìn)行了微縮或者更新為下一代版本,因此可編程再配置性能夠輕松地滿足電源要求的變化。

(17)可編程再配置性可輕松地滿足由于海量外圍存儲(chǔ)器和數(shù)字 LCD、LED或等離子顯示板等外接器件不斷變化的接口信號(hào)標(biāo)準(zhǔn)而導(dǎo)致的系統(tǒng)電源要求的變化。

PPS控制器 IC中實(shí)現(xiàn)的具體功能:

為了確保您能夠選擇一款具有低風(fēng)險(xiǎn)降低優(yōu)勢(shì)的 PPS控制器 IC,可參照下列具體的特征:

(1)充足數(shù)量的頻道通道,以滿足系統(tǒng)需求,以便 PPS控制器 IC能夠完成整個(gè)工作;

(2)每個(gè)通道電壓輸出和過(guò)電流設(shè)置值均可編程;

(3)每個(gè)通道停機(jī)能力可編程,以執(zhí)行各種節(jié)電方案;

(4)即便系統(tǒng)關(guān)機(jī)或者處于休眠模式,仍保持需要接收電源的系統(tǒng)區(qū)段的線性穩(wěn)壓器帶電;

(5)直觀易用的設(shè)計(jì)和配置軟件;

(6)對(duì)元件隨時(shí)間和溫度出現(xiàn)的偏移不敏感;

(7)采用芯片內(nèi) PROM的內(nèi)置自動(dòng)自配置;

(8)對(duì)關(guān)鍵參數(shù)的簡(jiǎn)單數(shù)字化外部控制,從通道電源電壓開(kāi)始;

(9)可方便地通過(guò)外部主機(jī)處理器讀取控制器狀態(tài);

(10)完全集成的過(guò)電壓保護(hù)、欠電壓閉鎖和過(guò)電流保護(hù);

(11)自動(dòng)電壓饋送勻變定時(shí)和排序;

(12)可編程復(fù)位定時(shí),電源良好,啟用門(mén)控和延時(shí)。

恰如其分的 PPS控制器 IC

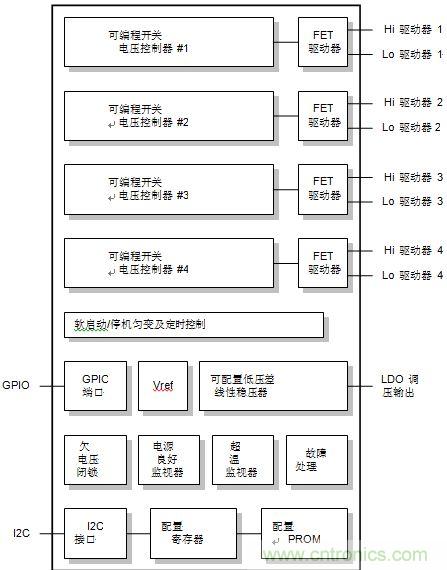

圖2所示為 PPS控制器 IC的簡(jiǎn)化框圖,它擁有所有優(yōu)點(diǎn)并且滿足上述所有準(zhǔn)則。圖形所示為 Exar XRP7714和 XRP7740、兩針兼容 PPS控制器 IC的方框圖。

圖2, XRP7714/7740 PPS控制器方框圖

XRP7714和 XRP7740 PPS控制器 IC結(jié)合了執(zhí)行5輸出 PPS所需的所有功能。芯片含四個(gè)可編程開(kāi)關(guān)電壓控制器以及集成的 FET驅(qū)動(dòng)器,可驅(qū)動(dòng)大電源和小電源 MOSFET,以每通道2A~20A的電流生成開(kāi)關(guān)電源,XRP7740擁有更大電源的門(mén)驅(qū)動(dòng)器。大電源MOSFET和幾個(gè)額外的無(wú)源器件便是在四種不同的可編程電源電壓下執(zhí)行四個(gè)高電流開(kāi)關(guān)電源操作所需的一切。XRP7714和 XRP7740也包含了一個(gè)可配置的線性100mA低壓差線性(LDO)穩(wěn)壓器,可提供第五種系統(tǒng)電源電壓(3.3或5V)??墒褂每膳渲肔DO穩(wěn)壓器作為必須保持加電的系統(tǒng)元件的保持電源,系統(tǒng)其余部分?jǐn)嚯姟?/div>

除了可編程電源電壓之外,XRP7714和XRP7740還可以控制電壓供給的加電和斷電特征。它可獨(dú)立控制四個(gè)電壓通道中每一個(gè)通道的勻變速度,并且可以控制電源電壓之間的相對(duì)定時(shí)。最后一個(gè)特征能夠讓系統(tǒng)設(shè)計(jì)師依照FPGA、介質(zhì)處理器、ASIC、SoC和ASSP等眾多復(fù)雜邏輯IC的要求創(chuàng)建更高級(jí)的電源電壓。

XRP7714和XRP7740也合并有多個(gè)系統(tǒng)管理功能,這些功能與電源有關(guān),包括欠電壓和電源良好監(jiān)控、超溫運(yùn)行及故障處理。所有系統(tǒng)監(jiān)視器均可配置,并且可以經(jīng)由芯片的 I2C接口,由主機(jī)處理器對(duì)其狀態(tài)進(jìn)行查詢。

[page]

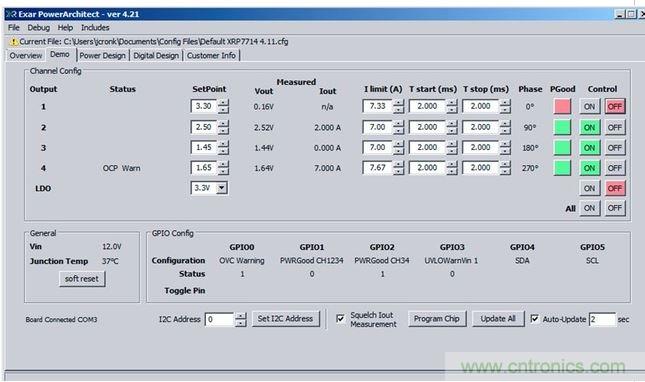

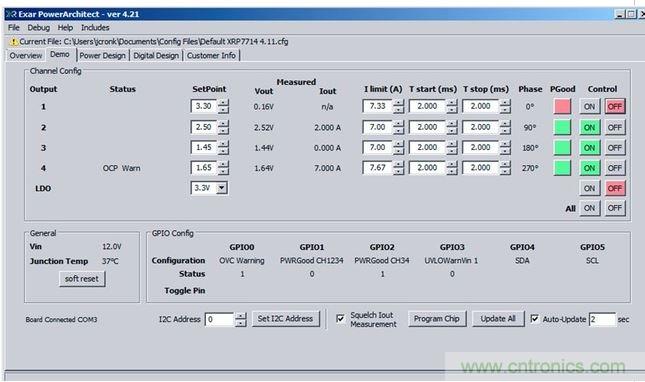

兩個(gè)器件的配置在一個(gè)名為 PowerArchitectTM的基于 PC的軟件程序中進(jìn)行。圖3所示為 PowerArchitectTM監(jiān)視屏的屏幕抓圖。該屏幕抓圖顯示了四個(gè)高電流開(kāi)關(guān)輸出以及電流限制和勻變定時(shí)參數(shù)的輸出電壓設(shè)置值(可依照輸出電壓配置為 50mV或 100mV)。

圖3,針對(duì) XRP7714配置的 PowerArchitectTM屏幕截圖。

輸入到 PowerArchitectTM中的配置數(shù)據(jù)起兩個(gè)重要作用。首先,它驅(qū)動(dòng)嵌入到Digital Power Studio中的自動(dòng) BOM生成器來(lái)創(chuàng)建制造PPS所需的完整元件清單,該清單包括部件號(hào)和廠商建議。其次,配置參數(shù)確定了 XRP7714和 XRP7740中配置寄存器中的配置設(shè)定值??山?jīng)由芯片的 I2C輸入,從芯片內(nèi) PROM或者從外部信源對(duì)這些配置寄存器進(jìn)行初始化。

結(jié)論

Exar的可編程 XRP7714和 XRP7740 PPS控制器 IC構(gòu)成了 PPS的核心,它可以處理系統(tǒng)電源電壓所造成的眾多不確定性,而無(wú)需對(duì)硬件設(shè)計(jì)進(jìn)行后期修正。還可以有效地處理在產(chǎn)品制造出廠后突然出現(xiàn)的眾多與電源相關(guān)的問(wèn)題,只需下載代碼即可。采用 PPS控制器 IC來(lái)創(chuàng)建可編程電源的優(yōu)勢(shì)類似于在現(xiàn)場(chǎng)采用系統(tǒng)電源而不是邏輯對(duì)處理器固件進(jìn)行升級(jí)。這些優(yōu)勢(shì)有助于在未來(lái)對(duì)系統(tǒng)設(shè)計(jì)進(jìn)行升級(jí)。Exar的 PowerXR產(chǎn)品系列包括 XRP7714、XRP7740和XRP7724,使得 PPS的設(shè)計(jì)方便、簡(jiǎn)單、快捷、靈活。