【導(dǎo)讀】為了滿足智能手機功能日益提高的數(shù)據(jù)需求,現(xiàn)代數(shù)字移動通信系統(tǒng)的基礎(chǔ)設(shè)施必須持續(xù)發(fā)展以支持更寬的帶寬和更快的數(shù)據(jù)轉(zhuǎn)換。為實現(xiàn)高速的數(shù)據(jù)速率,數(shù)字轉(zhuǎn)換器中的數(shù)字中頻處理、包括DDC(數(shù)字下變頻器)和DUC(數(shù)字上變頻器)是其中主要的功能模塊。

這些數(shù)字功能可在DSP和FPGA中實現(xiàn),某些大公司也會構(gòu)建自己的數(shù)字中頻處理ASIC。ADI公司正在將越來越多的此類數(shù)字中頻處理模塊集成到高速轉(zhuǎn)換器IC中,從而大幅減輕設(shè)計工作,節(jié)省系統(tǒng)成本和功耗。本文探討ADI公司IF和RF轉(zhuǎn)換器中的集成DDC和DUC通道,并說明它們在實際應(yīng)用中如何工作。

高速轉(zhuǎn)換器是現(xiàn)代無線基站系統(tǒng)的關(guān)健功能之一。越來越多的此類轉(zhuǎn)換器集成了復(fù)雜的數(shù)字信號處理模塊,以便簡化系統(tǒng)設(shè)計中的FPGA工作。轉(zhuǎn)換器中的數(shù)字信號處理模塊對系統(tǒng)設(shè)計非常有益,但這些益處尚未得到很多工程師的全面了解。希望本文能給數(shù)據(jù)轉(zhuǎn)換器中的DDC和DUC功能做一個清楚的說明,使系統(tǒng)設(shè)計人員能充分利用ADI轉(zhuǎn)換器給收發(fā)器架構(gòu)帶來的好處。注意:本文將聚焦于ADC和DAC中的數(shù)字處理模塊;因此,某些描述中將發(fā)射機和接收機模塊加以合并。請忽略可能引起混淆的信號流向。

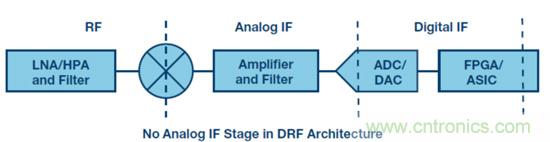

在現(xiàn)代數(shù)字移動通信系統(tǒng)中,發(fā)射和接收路徑(包括下面描述中的反饋接收路徑)可根據(jù)信號特性分為三個主要電路級:射頻級、模擬中頻級和數(shù)字中頻級。圖1是典型發(fā)射機和接收機的框圖。射頻級處理射頻信號,在當前LTE標準中,其信號頻率范圍一般是700 MHz到3.8 GHz。

經(jīng)過混頻器、調(diào)制器或解調(diào)器—這些都是混頻單元—處理后,射頻信號移動到DC至300 MHz以下的較低頻率。從數(shù)據(jù)轉(zhuǎn)換器到混頻器的處理模塊包括轉(zhuǎn)換器(ADC或DAC)、模擬濾波器和中頻放大器。我們可以把該級稱為模擬中頻級。

轉(zhuǎn)換器之后(事實上是在轉(zhuǎn)換器的量化器部分之后),信號變?yōu)閿?shù)字信號;它與隨后的FPGA或ASIC一起,我們稱之為數(shù)字中頻級。對于此級中的各數(shù)字信號處理模塊,在Tx路徑中通常稱之為DUC(數(shù)字上變頻器),在Rx路徑中通常稱之為DDC(數(shù)字下變頻器)。

直接射頻架構(gòu)是例外,其中數(shù)據(jù)轉(zhuǎn)換器直接對射頻信號采樣,因而沒有模擬中頻級,信號鏈僅由射頻級和數(shù)字中頻級構(gòu)成。

圖1.發(fā)射機或接收機的典型框圖。

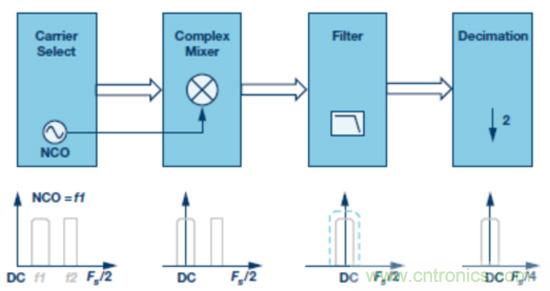

典型DDC模塊包括載波選擇、下變頻器、濾波器和抽取器。這些功能模塊按順序工作,或者可分別予以旁路,最終根據(jù)后續(xù)FPGA或ASIC(其采樣速率較低)的要求,產(chǎn)生一個位于DC的復(fù)信號或一個實信號。

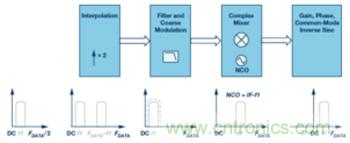

典型DUC模塊包括插值、濾波器、上變頻器和載波合并器。根據(jù)系統(tǒng)架構(gòu)設(shè)計,DUC產(chǎn)生一個位于DC的復(fù)信號或中頻信號,或者直接產(chǎn)生射頻信號。DUC的處理幾乎與DDC的處理相反。

常常將多個DDC和DUC級級聯(lián)以提供靈活性。獨立的DDC和DUC需要并行處理多個載波,合并之后輸出發(fā)射信號或在接收信號中將其分離。

DDC

Rx鏈路需要較高采樣速率以避免信號混疊,簡化模擬濾波器設(shè)計,提供更寬的信號頻帶。但另一方面,為了節(jié)省功耗、成本以及FPGA/ASIC中的高速邏輯,最好降低接口上的數(shù)據(jù)速率。轉(zhuǎn)換器的集成DDC將解決上述要求。圖2是典型DDC的框圖。

圖2.DDC框圖

NCO和混頻器

為了從干擾(阻塞信號和其他載波)中選擇所需的載波,NCO的輸出頻率與輸入中頻信號混頻以將所需載波頻移到DC。這樣可以降低后續(xù)濾波和抽取級的復(fù)雜度。

濾波和抽取

在NCO和混頻級之后,使用一個低通濾波器來選取所需的濾波并抑制其他不需要的信號。濾波器之后,使用一個2倍抽取器來降低數(shù)據(jù)速率。為了節(jié)省資源并向客戶提供靈活性,半帶FIR濾波器加2倍抽取器被合并在一個模塊中;重復(fù)使用該模塊以級聯(lián)三到四級。系統(tǒng)設(shè)計者可根據(jù)應(yīng)用需要選擇使用其中的一部分或全部。轉(zhuǎn)換器也可能提供2倍之外的其它抽取率以提供更大的靈活性,尤其是在RF ADC中。

DUC

Tx鏈具有與Rx鏈相同的要求:需要高采樣速率以簡化濾波器設(shè)計,使信號頻率位于高中頻或直接變?yōu)樯漕l,以及遠遠地推開鏡像,但接口希望使用較低的數(shù)據(jù)速率。轉(zhuǎn)換器的集成DUC將解決這些要求。圖3是典型DUC的框圖。

插值和濾波

最簡單的數(shù)字插值算法稱為“零填充”,即在每兩個樣本之間插入0。采樣速率加倍,但在得到的頻譜中也會產(chǎn)生頻率為Fs –Fif的鏡像。因此,在插值器之后需要使用一個濾波器級,以便消除鏡像或原始載波(依據(jù)應(yīng)用而定)。如果消除的是原始載波,結(jié)果將是插值和Fs/2的粗調(diào)。

像在DDC中一樣,2倍插值和濾波器被合并為一個模塊。然后重復(fù)此功能模塊并級聯(lián)三到四級,以提高靈活性。也可使用2倍之外的其他插值系數(shù)以提供更大的靈活性,尤其是在RF DAC中。

NCO和混頻器

DUC中的NCO和混頻器級與DDC中的相同模塊非常相似,但功能相反,即根據(jù)系統(tǒng)架構(gòu)的要求,將載波頻移到所需的中頻或射頻頻率。在零中頻架構(gòu)中,可旁路此模塊以使載波保持在DC。

增益、相位、I/Q偏移和反Sinc

增益、相位調(diào)整、I/Q偏移和反sinc模塊是許多IF/RF DAC的附件。

增益、相位調(diào)整和I/Q偏移常常一起使用以獨立調(diào)諧輸出信號I/Q通道,補償不同類型的I/Q失配(DAC、模擬濾波器和調(diào)制器引起),最終從模擬調(diào)制器后輸出一個低本振泄漏和低鏡像的理想復(fù)信號。

圖3.DUC框圖

反sinc濾波器補償DAC引起的sinc滾降,這種滾降會影響平坦度和信號幅度,尤其是在采用高中頻或直接射頻架構(gòu)的寬帶應(yīng)用中。

總結(jié)

本文簡要說明了當前IF/RF轉(zhuǎn)換器中集成的典型DDC和DUC——它們是何物,為何需要它們,以及它們在信號鏈中如何工作。適當了解這些內(nèi)容并正確使用它們將能減少資源占用并減輕FBGA/ASIC中的編碼工作,以及節(jié)省系統(tǒng)的功耗和成本。