【導(dǎo)讀】本文第一部分詳細(xì)描述該基帶處理器的一般設(shè)計(jì)原則。該部分主要是BBP的理論介紹。在第二部分�,使用ADI公司的AD9361FPGA參考設(shè)計(jì)討論BBP的實(shí)際硬件實(shí)施。值得注意的是�,主要設(shè)計(jì)目標(biāo)是使設(shè)計(jì)盡可能簡(jiǎn)單,并在實(shí)驗(yàn)室環(huán)境中演示快速無(wú)線數(shù)據(jù)傳輸���。在使用和干擾RF頻譜時(shí)����,須考慮到法規(guī)及其他影響��。

如今����,無(wú)線系統(tǒng)無(wú)處不在,無(wú)線設(shè)備和服務(wù)的數(shù)量持續(xù)增長(zhǎng)����。設(shè)計(jì)完整的RF系統(tǒng)是一項(xiàng)跨學(xué)科設(shè)計(jì)挑戰(zhàn),模擬RF前端是其中最關(guān)鍵的部分���。然而��, AD9361 等集成RF收發(fā)器的推出顯著減少了此類設(shè)計(jì)的RF挑戰(zhàn)�。這些收發(fā)器可為模擬RF信號(hào)鏈提供數(shù)字接口,允許輕松集成到ASIC或FPGA�����,進(jìn)行基帶處理�。基帶處理器(BBP)允許在終端應(yīng)用和收發(fā)器設(shè)備之間的數(shù)字域中處理用戶數(shù)據(jù)���。此外�����,使用Simulink等系統(tǒng)建模工具可以輕松完成基帶處理器設(shè)計(jì)��。然而���,新手用戶可能會(huì)發(fā)現(xiàn)難以理解和解決這個(gè)通信系統(tǒng)難題。本文嘗試為無(wú)線傳輸通信系統(tǒng)設(shè)計(jì)和實(shí)施簡(jiǎn)單的RF基帶處理器�。設(shè)計(jì)使用AD9361 FPGA參考設(shè)計(jì)框架����,在AD-FMCOMMS2-EBZ和Xilinx® ZC706平臺(tái)上實(shí)施�����。

基本設(shè)計(jì)

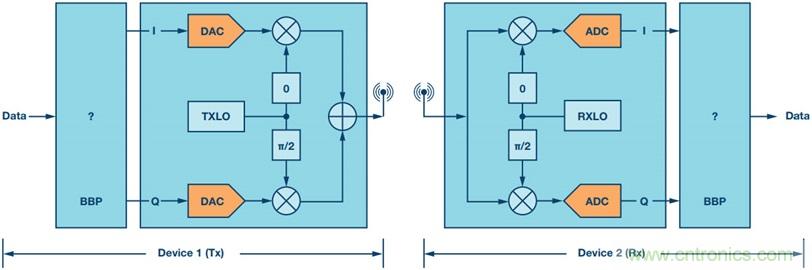

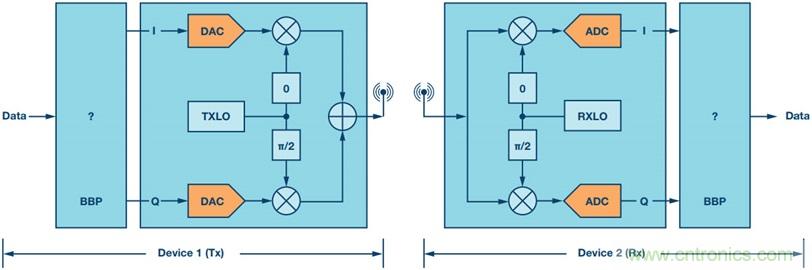

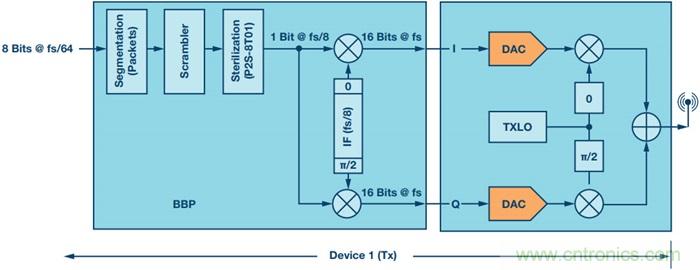

典型的RF系統(tǒng)如圖1所示,直接RF系統(tǒng)除外���。該圖1僅顯示了單個(gè)數(shù)據(jù)路徑�,反方向是該數(shù)據(jù)路徑的鏡像圖像�����。本文中提出的相關(guān)基帶處理器允許對(duì)數(shù)據(jù)進(jìn)行處理�����,以使其在兩個(gè)RF系統(tǒng)之間進(jìn)行無(wú)線傳輸�。下文討論了基本設(shè)計(jì)要求。

圖1. RF系統(tǒng)框圖

在兩個(gè)正交信號(hào)I & Q上重復(fù)數(shù)據(jù)

注意����,載波相互獨(dú)立且彼此不同步。因此�,發(fā)射和接收載波之間存在相位和頻率偏移。這將對(duì)接收器的解調(diào)產(chǎn)生不利影響��。一個(gè)重要問(wèn)題是信號(hào)反轉(zhuǎn),正交信號(hào)可能會(huì)反轉(zhuǎn)其作用�����,因?yàn)槠茣?huì)定期合并和漂離����。克服這種不確定性的簡(jiǎn)單方法是在兩個(gè)正交信號(hào)上重復(fù)相同數(shù)據(jù)���。

以串行形式發(fā)送和接收數(shù)據(jù)(按位)

大多數(shù)情況下��,與BBP連接的RF前端接口是DAC和ADC���。這些是模擬信號(hào)的數(shù)字接口。因此�����,不能簡(jiǎn)單地將數(shù)據(jù)發(fā)送到DAC輸入����,并預(yù)計(jì)在ADC輸出端獲得相同數(shù)據(jù)。數(shù)據(jù)以串行形式發(fā)射��,將單個(gè)位數(shù)據(jù)映射到DAC的全部分辨率。同樣���,數(shù)據(jù)以串行形式接收���,從ADC的全部分辨率解映射。這提供了充足的冗余��。如果這些是16位轉(zhuǎn)換器��,則接收器將從可能的65536數(shù)據(jù)集中決定1或0����。僅這一點(diǎn)�,便可以顯著簡(jiǎn)化解碼。

I & Q信號(hào)相互正交

RF前端設(shè)備(如AD9361)是I/Q收發(fā)器���。如果輸入是正交信號(hào)��,這些設(shè)備最有效�。這些設(shè)備通常沿兩個(gè)數(shù)據(jù)路徑進(jìn)行內(nèi)部I/Q匹配和校正���,以抵消二者之間的任何差異����。規(guī)則是,實(shí)部(I)信號(hào)是余弦函數(shù)�,虛部(Q)信號(hào)是正弦函數(shù)。

調(diào)制方案是BPSK

可以部署信號(hào)幅度��、頻率或相位調(diào)制的所有常見(jiàn)方法�����。檢測(cè)相位差異相對(duì)來(lái)說(shuō)更加簡(jiǎn)單�����。由于數(shù)據(jù)以串行形式傳輸�����,因此必然會(huì)選擇二進(jìn)制相移鍵控(BPSK)�����。

位間隔是8個(gè)樣本

數(shù)據(jù)需要時(shí)序信息���,位間隔����。可能的最大位間隔是采樣周期��。為了使接收器保持簡(jiǎn)單��,需要足夠的時(shí)間來(lái)解碼信號(hào)并做出決定��。最簡(jiǎn)單的時(shí)序恢復(fù)方法是零交越和峰值檢測(cè)���。在這種情況下,峰值將不一致�。因此,選擇零交越進(jìn)行位間隔檢測(cè)和跟蹤����。兩種系統(tǒng)之間也存在載波差異。在某些情況下�����,在用戶數(shù)據(jù)的任意端�����,樣本可能模糊不清。為每半個(gè)正弦信號(hào)留出4個(gè)樣本��,位間隔設(shè)置為8個(gè)樣本����。因此,有效的傳輸速率是采樣頻率除以8��。

數(shù)據(jù)沒(méi)有直流成分

時(shí)序和相對(duì)相位恢復(fù)以信號(hào)的零交越為基礎(chǔ)��。因此���,單個(gè)信號(hào)需要不含任何直流成分�����。此外�����,要求信號(hào)每隔一個(gè)位間隔允許至少一個(gè)零交越�����。正弦信號(hào)兼具兩者的屬性��,并且非常符合上述BPSK調(diào)制方案要求��。

數(shù)據(jù)已加擾

用戶數(shù)據(jù)是任意的很可能是一長(zhǎng)串1或0�����。數(shù)據(jù)需要加擾�,以便在接收器端恢復(fù)時(shí)序和相位,從而更高效地跟蹤信號(hào)�。

數(shù)據(jù)以數(shù)據(jù)包的形式傳輸

由于系統(tǒng)彼此不同步,因此接收器的信號(hào)會(huì)存在幅度���、頻率和相位誤差�����。解調(diào)信號(hào)是發(fā)射信號(hào)相對(duì)于本地載波發(fā)生相位變化的信號(hào)。載波可能會(huì)跟蹤一段時(shí)間����,選取數(shù)據(jù),然后再跟蹤�。因此,設(shè)計(jì)需要做好部分?jǐn)?shù)據(jù)丟失的準(zhǔn)備�����。為此,數(shù)據(jù)以數(shù)據(jù)包的形式傳輸���?����?芍貜?fù)傳輸多個(gè)數(shù)據(jù)包��,而非整個(gè)數(shù)據(jù)��。

使用CRC驗(yàn)證數(shù)據(jù)包

數(shù)據(jù)包攜帶循環(huán)冗余校驗(yàn)(CRC)碼�,因此如果存在不匹配���,則允許接收器丟包�����,并請(qǐng)求再次發(fā)送�。

在每個(gè)前同步碼期間完成時(shí)序和相位校正

數(shù)據(jù)包表頭攜帶前同步碼�����,用于將其從接收到的數(shù)據(jù)流中劃分出來(lái)。此外�,接收器使用該前同步碼復(fù)位信號(hào)的時(shí)序和相位信息,以解調(diào)數(shù)據(jù)包數(shù)據(jù)����。

內(nèi)置性能指標(biāo)

接收器也支持統(tǒng)計(jì)計(jì)數(shù)器,如接收到的����、丟棄的或校正的數(shù)據(jù)包數(shù)量。這些計(jì)數(shù)器用于衡量和監(jiān)控性能指標(biāo)���,包括誤碼率和有效數(shù)據(jù)速率�����。

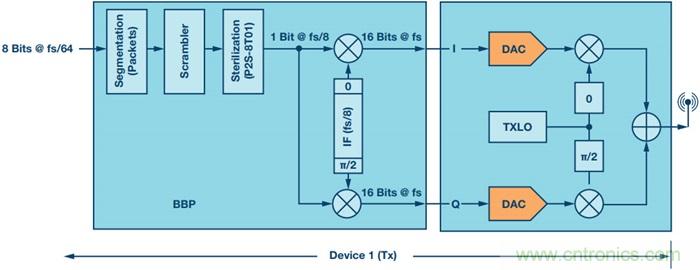

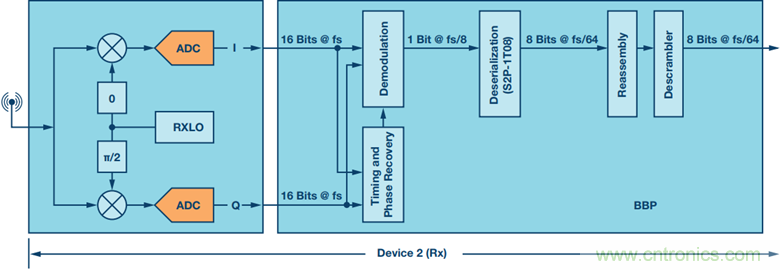

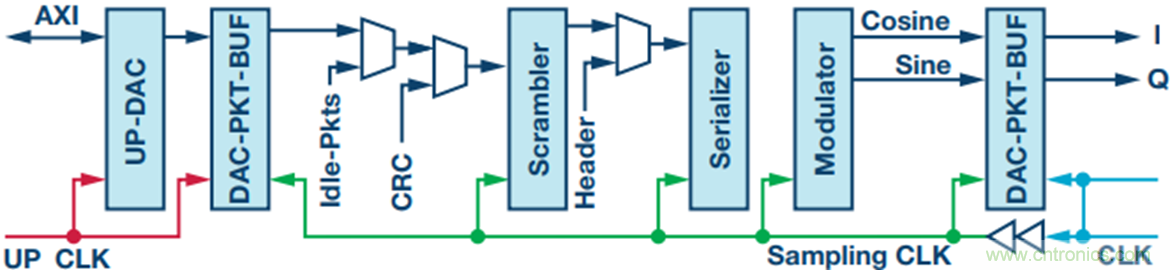

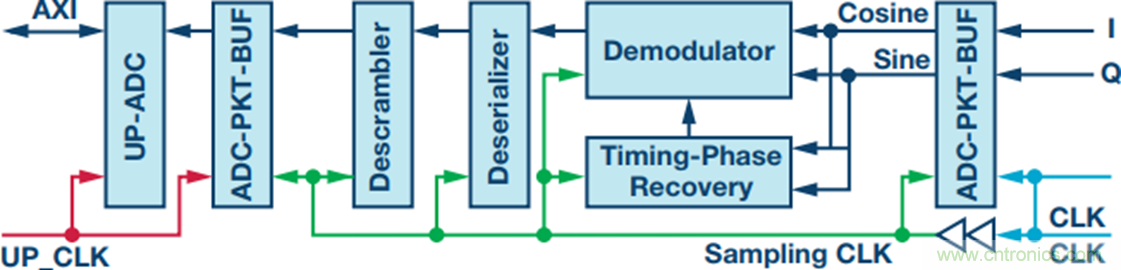

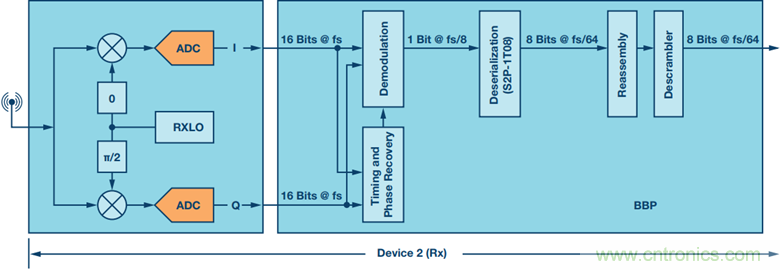

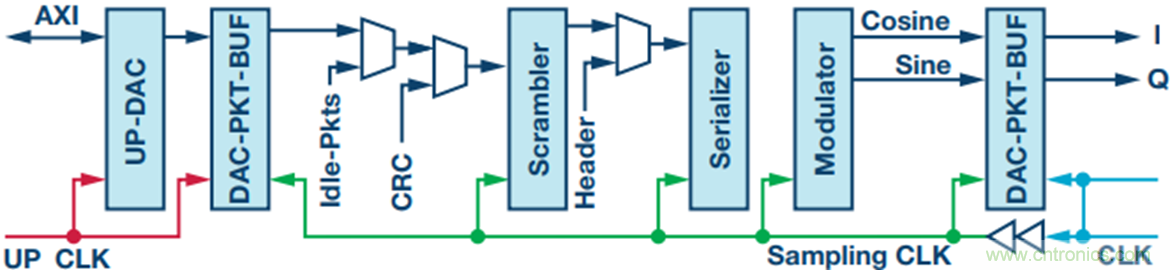

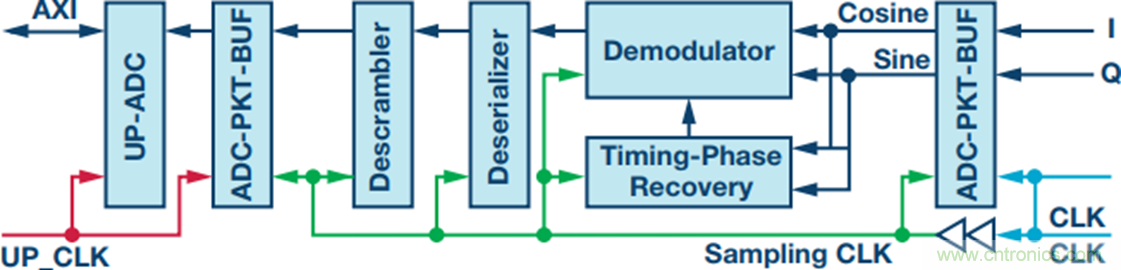

總而言之����,數(shù)據(jù)作為數(shù)據(jù)包以串行形式發(fā)送和接收����。數(shù)據(jù)包攜帶前同步碼和CRC。數(shù)據(jù)在收發(fā)器設(shè)備前的中間正交信號(hào)上經(jīng)過(guò)BPSK調(diào)制和解調(diào)�����。因此��,中間信號(hào)頻率和數(shù)據(jù)的位速率是采樣速率的八分之一���?���;鶐幚砥髂K及上述設(shè)計(jì)細(xì)節(jié)如圖2和3所示���。

圖2. BBP發(fā)送功能框圖

圖3. BBP接收功能框圖

發(fā)送器讀取數(shù)據(jù)字節(jié)(字符寬度)�����,并將其轉(zhuǎn)換為帶有表頭或前同步碼的數(shù)據(jù)包�。將CRC添加到數(shù)據(jù)包末端���。然后���,對(duì)數(shù)據(jù)包數(shù)據(jù)進(jìn)行加擾和串行處理�。在連接到收發(fā)器之前�����,單個(gè)位數(shù)據(jù)相位調(diào)制余弦(I)和正弦(Q)函數(shù)��。

在接收方向�����,離線模塊恢復(fù)并跟蹤時(shí)序間隔和調(diào)制信號(hào)的相對(duì)相位����。該信息用于從輸入的ADC樣本中恢復(fù)串行數(shù)據(jù)。然后組裝到數(shù)據(jù)包�����,并進(jìn)行解擾�。在數(shù)據(jù)包結(jié)束時(shí),比較CRC��,如果不匹配����,則丟棄數(shù)據(jù)包。如果CRC匹配��,數(shù)據(jù)傳遞給終端用戶�。

實(shí)現(xiàn)

BBP設(shè)計(jì)在硬件中實(shí)施和測(cè)試。硬件是兩個(gè)評(píng)估板的組合:具有Zynq FPGA設(shè)備的Xilinx ZC706評(píng)估板����,以及具有AD9361收發(fā)器的AD-FMCOMMS3-EBZ評(píng)估板。ADI提供支持該硬件的完整參考設(shè)計(jì)�。該開(kāi)源設(shè)計(jì)在主要工具版本中免費(fèi)提供,可獲得完全支持和更新����。硬件詳細(xì)信息參見(jiàn)下列URL:

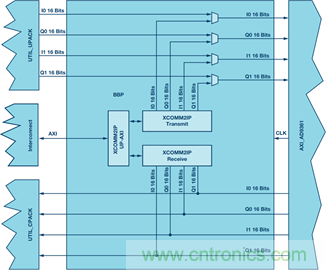

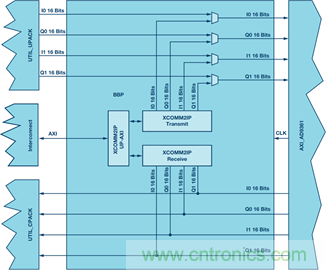

ADI參考設(shè)計(jì)是支持Linux®框架的嵌入式系統(tǒng)。包含圍繞ARM®處理器的各種外設(shè)�。AD9361設(shè)備連接到 axi_AD9361 IP外設(shè)。它在RF設(shè)備和系統(tǒng)存儲(chǔ)器之間傳輸原始采樣數(shù)據(jù)���。

外設(shè)和設(shè)備通過(guò)Linux內(nèi)核驅(qū)動(dòng)程序進(jìn)行初始化和控制��。BBP則作為連接到 axi_AD9361的另一個(gè)IP外設(shè)��。出于歷史原因���,BBP IP命名為 axi_xcomm2ip ����。Linux中的用戶空間應(yīng)用程序用于在系統(tǒng)之間控制�、發(fā)送和接收數(shù)據(jù)。

在ADI參考設(shè)計(jì)中���,在發(fā)送方向�,axi_AD9361 IP連接到解包模塊(util_upack)����,在接收方向,連接到打包模塊(util_cpack)�����。 在發(fā)送方向����,BBP數(shù)據(jù)插入解包模塊和AD9361內(nèi)核之間。為了使其不影響默認(rèn)數(shù)據(jù)路徑�����,BBP支持可選的數(shù)據(jù)路徑多路復(fù)用器��,以選擇解包數(shù)據(jù)源或BBP數(shù)據(jù)源。BBP允許參考設(shè)計(jì)數(shù)據(jù)路徑作為默認(rèn)路徑��,并僅在啟用時(shí)選擇BBP數(shù)據(jù)源�����。在接收方向�,BBP僅連接到AD9361內(nèi)核���。參考設(shè)計(jì)數(shù)據(jù)路徑不受影響����。這允許框架不受妨礙地引導(dǎo)和設(shè)置系統(tǒng)�����。在系統(tǒng)設(shè)置后�,啟用BBP,可通過(guò)覆蓋默認(rèn)數(shù)據(jù)路徑來(lái)進(jìn)行數(shù)據(jù)傳輸�����。以ADI參考設(shè)計(jì)實(shí)施的BBP的框圖如圖4所示�。

圖4. BBP IP框圖

本文中討論的設(shè)計(jì)��、初始化和數(shù)據(jù)傳輸使用一對(duì)這種硬件����。設(shè)置僅需一對(duì)HDMI®監(jiān)視器�����、鍵盤(pán)和鼠標(biāo)及天線����。系統(tǒng)彼此完全不同步,但需要相同設(shè)置����。在每個(gè)方向,數(shù)據(jù)在不同載波上傳輸���。設(shè)備1的發(fā)射載波頻率和設(shè)備2的接收載波頻率相同����,但在另一個(gè)方向上不同�����。然而,如果回送中使用單個(gè)設(shè)備�����,發(fā)射和接收載波必須具有相同的頻率����。BBP的HDL設(shè)計(jì)采用ADI庫(kù)模塊��。

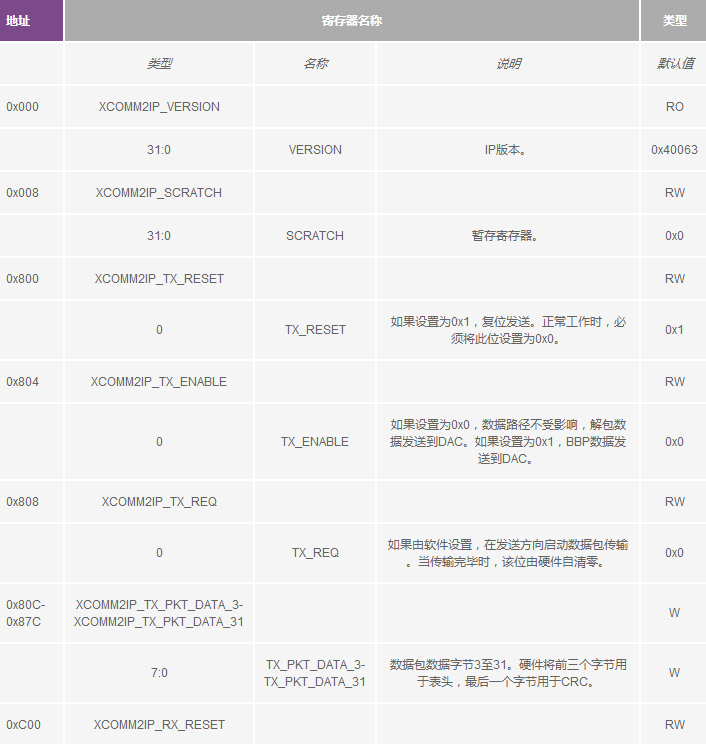

控制(微處理器)接口

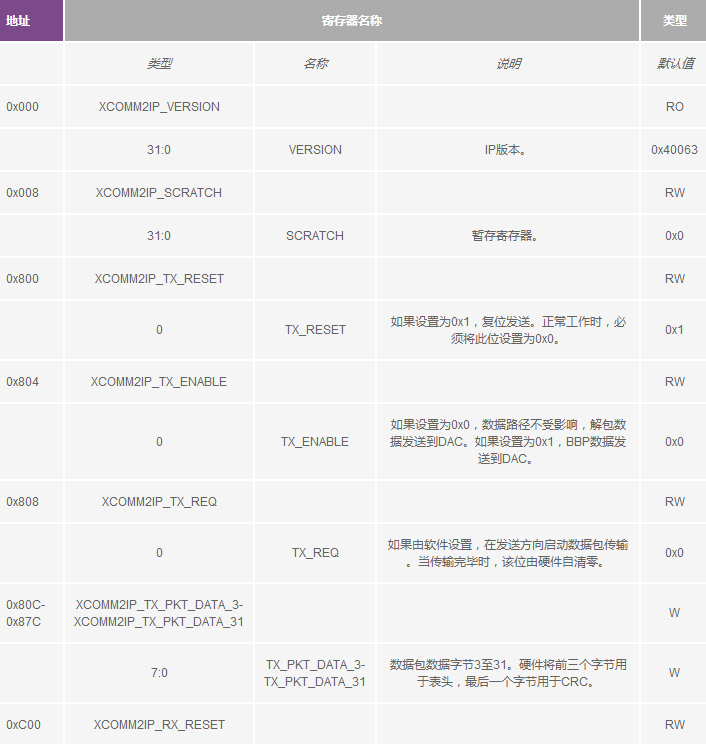

AXI-Lite接口用于通過(guò)處理器控制和監(jiān)控BBP�����。使用ADI公共庫(kù)(hdl/library/common/up_axi.v)中的up_axi模塊�,可以輕松推斷該接口模塊。該模塊將AXI-Lite接口轉(zhuǎn)換為簡(jiǎn)單內(nèi)存��,如讀取和寫(xiě)入總線��。和任何其他ADI IP一樣�����,添加內(nèi)部寄存器和內(nèi)存。寄存器映射如表1所示����。

表1. BBP寄存器映射

up_axi: 模塊端口及其端口映射如下所述。

up_rstn: AXI接口復(fù)位(異步低電平有效)���,連接到 s_axi_aresetn.

up_clk: AXI接口時(shí)鐘����,連接到 s_axi_aclk.

up_axi_*: AXI接口信號(hào)����,連接到等效 s_axi_* 端口

up_wreq, up_waddr, up_wdata, up_wack: 內(nèi)部寫(xiě)入接口, the up_wreq 信號(hào)與地址和數(shù)據(jù)一同置位����,以指示寫(xiě)入請(qǐng)求。請(qǐng)求需要通過(guò)up_wack 端口應(yīng)答�����。

如下所示��,實(shí)施簡(jiǎn)單的寄存器寫(xiě)入����。

always @(negedge up_rstn or posedge up_clk)

begin

if (up_rstn == 0) begin

up_wack <= ''d0;

up_reg0 <= UP_REG0_RESET_VALUE;

end else begin

up_wack <= up_wreq_s;

if ((up_wreq_s == 1''b1) && (up_waddr == UP_ REG0_ADDRESS)) begin

up_reg0 <= up_wdata[UP_REG0_WIDTH-1:0];

end

end

end

模塊在二者之間執(zhí)行地址轉(zhuǎn)換����。AXI接口使用字節(jié)地址�,但內(nèi)部總線使用DWORD地址。結(jié)果是��,up_axi模塊丟棄AXI地址的兩個(gè)最低有效位���,以生成內(nèi)部DWORD地址�。

up_rreq, up_raddr, up_rdata, up_rack: 內(nèi)部讀取接口����, up_rreq 信號(hào)與地址一同置位��,以指示讀取請(qǐng)求����。請(qǐng)求需要與讀取數(shù)據(jù)一同通過(guò) up_rack 端口應(yīng)答。

如下所示��,實(shí)施與上述相同的寄存器用于讀取��。

always @(negedge up_rstn or posedge up_clk)

begin

if (up_rstn == 0) begin

up_rack <= ''d0;

up_rdata <= ''d0;

end else begin

up_rack <= up_rreq_s;

if ((up_rreq_s == 1''b1) && (up_raddr == UP_ REG0_ADDRESS)) begin

up_rdata <= up_reg0;

end else begin

up_rdata <= 32''d0;

end

end

end

相同地址轉(zhuǎn)換也適用于讀取。讀取數(shù)據(jù)僅在請(qǐng)求時(shí)驅(qū)動(dòng)�����,否則設(shè)置為零�����。這是因?yàn)閡p_axi模塊將單個(gè)讀取數(shù)據(jù)從各個(gè)地址組傳遞到OR門(mén)����。因此,未選擇的地址組需要驅(qū)動(dòng)讀取數(shù)據(jù)零�����。

如上方寄存器映射表中所列����,BBP有三個(gè)地址空間。常見(jiàn)寄存器空間映射至0x000�、發(fā)送(DAC)映射至0x800 (0x200),接收(ADC)映射至0xC00 (0x300)��。軟件(Linux用戶空間應(yīng)用程序)應(yīng)當(dāng)將發(fā)送數(shù)據(jù)包數(shù)據(jù)寫(xiě)入緩沖器���,并從另一個(gè)緩沖器中讀取接收到的數(shù)據(jù)包數(shù)據(jù)�。數(shù)據(jù)包大小選擇為32字節(jié),帶有3字節(jié)前同步碼和1字節(jié)CRC�����。

數(shù)據(jù)接口

對(duì)于接收和發(fā)送方向的兩個(gè)通道��,AD9361接口內(nèi)核包含兩對(duì)16位I/Q數(shù)據(jù)��。內(nèi)核按照與AD9361數(shù)字接口相同的時(shí)鐘運(yùn)行���。在2R2T模式下�,這是采樣速率的4倍����。在1R1T模式下,這是采樣速率的2倍���。有效數(shù)據(jù)速率由有效信號(hào)控制。因此在2R2T模式下��,每4個(gè)時(shí)鐘置位一次有效����。在1R1T模式下��,每2個(gè)時(shí)鐘置位一次有效�。BBP旨在支持2R2T和1R1T模式�����。它使用單個(gè)發(fā)送和接收通道����。內(nèi)部邏輯在2R2T和1R1T模式下以采樣速率運(yùn)行。然后�,BBP在其時(shí)鐘頻率下,通過(guò)接口內(nèi)核傳輸數(shù)據(jù)�����。這樣是為了在BBP內(nèi)演示時(shí)鐘轉(zhuǎn)換��。在許多情況下����,用戶可能希望無(wú)論收發(fā)器的接口速率如何,都能在采樣速率下運(yùn)行BBP邏輯��。

使用Xilinx基元BUFR和BUFG,生成采樣頻率內(nèi)部時(shí)鐘����。BUFR是分壓器,BUFG是高扇出時(shí)鐘緩沖器����。為此,也可以使用MMCM��。如下所示����,生成內(nèi)部時(shí)鐘。

parameter XCOMM2IP_1T1R_OR_2T2R_N = 0; localparam XCOMM2IP_SCLK_DIVIDE = (XCOMM2IP_1T1R_OR_2T2R_N == 1) ? "2" : "4";

BUFR #(.BUFR_DIVIDE(XCOMM2IP_SCLK_DIVIDE)) i_bufr (

.CLR (1''b0),

.CE (1''b1),

.I (clk),

.O (s_clk_s));

BUFG i_bufg (

.I (s_clk_s),

.O (s_clk));

使用BUFR和BUFG可確保時(shí)鐘頻率鎖定����,但會(huì)影響相位確定性。最大相位不確定性是單個(gè)接口時(shí)鐘周期��。通過(guò)帶有同步信號(hào)的四級(jí)寄存器陣列���,可以輕松補(bǔ)償該不確定性。然而�����,設(shè)計(jì)采用了雙端口RAM模塊來(lái)實(shí)現(xiàn)數(shù)據(jù)傳輸。這也是為了展示常見(jiàn)信號(hào)處理要求的應(yīng)用實(shí)例��。使用ADI庫(kù)內(nèi)存模塊(ad_mem)可以推斷出雙端口RAM元件���。

發(fā)送接口

在發(fā)送方向��,處理器將數(shù)據(jù)包數(shù)據(jù)寫(xiě)入緩沖器(參見(jiàn)上方寄存器映射表)���。然后,請(qǐng)求硬件發(fā)送該數(shù)據(jù)包����。BBP將數(shù)據(jù)包連續(xù)發(fā)送給設(shè)備。在數(shù)據(jù)包開(kāi)始時(shí)��,檢查是否有任何請(qǐng)求�����。如果沒(méi)有待處理的請(qǐng)求�,則發(fā)送空閑數(shù)據(jù)包。如果有請(qǐng)求等待處理���,讀取并發(fā)送數(shù)據(jù)包緩沖器�。

發(fā)送邏輯使用自由運(yùn)行位計(jì)數(shù)器,按照位寬運(yùn)行���。當(dāng)位計(jì)數(shù)器為0x0時(shí)��,更新緩沖器讀取地址�。由于在數(shù)據(jù)包傳輸期間可能會(huì)隨時(shí)出現(xiàn)處理器請(qǐng)求���,因此在數(shù)據(jù)包傳輸開(kāi)始時(shí)會(huì)立即捕獲并清零���。在數(shù)據(jù)包傳輸開(kāi)始時(shí),如果請(qǐng)求等待處理����,則應(yīng)答回至處理器接口。利用請(qǐng)求在緩沖器數(shù)據(jù)或空閑數(shù)據(jù)之間進(jìn)行選擇��。

圖5. 發(fā)送數(shù)據(jù)路徑

數(shù)據(jù)包數(shù)據(jù)的前兩個(gè)字節(jié)設(shè)置為0xfff0���。第三個(gè)字節(jié)用于表示空閑(0xc5)或數(shù)據(jù)(0xa6)數(shù)據(jù)包�。CRC字節(jié)作為數(shù)據(jù)包的最后一個(gè)字節(jié)插入。CRC多項(xiàng)式為x8 + x2 + x + 1��。除表頭外的所有字節(jié)已加擾����。加擾多項(xiàng)式與SONET/SDH (x7 + x6 + 1)相同��。

余弦和正弦查找表用于生成調(diào)制載波���。在8個(gè)樣本中���,位間隔等于完整的信號(hào)周期(0至2�)。位數(shù)據(jù)用于反轉(zhuǎn)信號(hào)�。然后,數(shù)據(jù)寫(xiě)入小緩沖器�����,并使用接口時(shí)鐘��,根據(jù)AD9361接口內(nèi)核中的有效信號(hào)讀取�。

接收接口

在接收方向,針對(duì)表頭模式0xfff0�����,監(jiān)控I/Q數(shù)據(jù)。這種獨(dú)特的模式在數(shù)據(jù)包傳輸中只出現(xiàn)一次�。可以發(fā)送數(shù)據(jù)包數(shù)據(jù)���,以使加擾器輸出重復(fù)該模式�����。軟件會(huì)限制并阻止該做法��。12個(gè)連續(xù)位間隔的該系列同相數(shù)據(jù)序列用于通過(guò)時(shí)序恢復(fù)模塊復(fù)位并跟蹤接收器時(shí)序和相位�����。因此�����,將復(fù)位其時(shí)序計(jì)數(shù)器并將其相位值設(shè)置為0x1�。該序列后的第一個(gè)反轉(zhuǎn)被視為0x0�����。在此之后,時(shí)序恢復(fù)模塊在整個(gè)數(shù)據(jù)包傳輸過(guò)程中保持其狀態(tài)不變���。

數(shù)據(jù)恢復(fù)模塊計(jì)算信號(hào)的平均值�,并決定信號(hào)的當(dāng)前相位��。然后�,與時(shí)序恢復(fù)模塊跟蹤的相對(duì)相位進(jìn)行比較��。如果發(fā)生沖突���,根據(jù)過(guò)去的信號(hào)變化做決定���。這是因?yàn)闆_突通常是由相位切換引起的。

圖6. 接收數(shù)據(jù)路徑

然后�����,解調(diào)的位數(shù)據(jù)組裝到字節(jié)�,并進(jìn)行解擾。如果傳輸緩沖器為空����,則數(shù)據(jù)寫(xiě)入傳輸緩沖器�。在數(shù)據(jù)包結(jié)束時(shí)驗(yàn)證CRC���。如果匹配且傳輸緩沖器已寫(xiě)入��,則通知處理器接口�。軟件應(yīng)當(dāng)監(jiān)控該請(qǐng)求���,如果已設(shè)置�,通過(guò)讀取其內(nèi)容來(lái)清空緩沖器����。然后,必須清除請(qǐng)求����,以便繼續(xù)進(jìn)行數(shù)據(jù)包傳輸。

構(gòu)建說(shuō)明和下載

本文介紹簡(jiǎn)單RF基帶處理器的理論和實(shí)施詳情����。討論了在ZC706和AD-FMCOMMS3-EBZ硬件上實(shí)現(xiàn)該設(shè)計(jì)的實(shí)際方案??焖傺菔竞蜆?gòu)建說(shuō)明的完整設(shè)計(jì)文件參見(jiàn)https://wiki.analog.com/resources/fpga/docs/hdl/xcomm2ip。此頁(yè)面也詳細(xì)介紹了HDL設(shè)計(jì)��、軟件、RF設(shè)置��、性能和分析�。

本文轉(zhuǎn)載自亞德諾半導(dǎo)體。

推薦閱讀: