【導(dǎo)讀】ADI專利的容性可編程增益放大器(PGA)相比傳統(tǒng)的阻性PGA具有更佳的性能���,包括針對模擬輸入信號的更高共模電壓抑制能力�。本文描述了斬波容性放大器的工作原理,強調(diào)了需要放大傳感器小信號至接近供電軌——比如溫度測量(RTD或熱電偶)和惠斯登電橋——時,此架構(gòu)的優(yōu)勢。

Σ-Δ型模數(shù)轉(zhuǎn)換器(ADC)廣泛用于傳感器具有較小輸出電壓范圍和帶寬的應(yīng)用中(比如應(yīng)變計或熱敏電阻)����,因為這種架構(gòu)提供高動態(tài)范圍。具有高動態(tài)范圍是因為���,相比其它ADC架構(gòu)��,它具有低噪聲性能����。

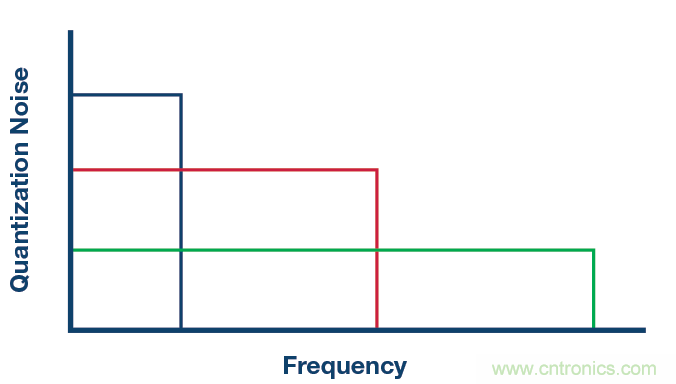

Σ-Δ型轉(zhuǎn)換器基于兩條原理工作:過采樣和噪聲整形�。當ADC對輸入信號進行采樣時,獨立于采樣頻率的量化噪聲會在直到采樣頻率一半的整個頻譜內(nèi)擴散���。因此�,如果輸入信號以比奈奎斯特理論所推導(dǎo)出的最小值高很多的頻率采樣,則目標頻段內(nèi)的量化噪聲下降�����。

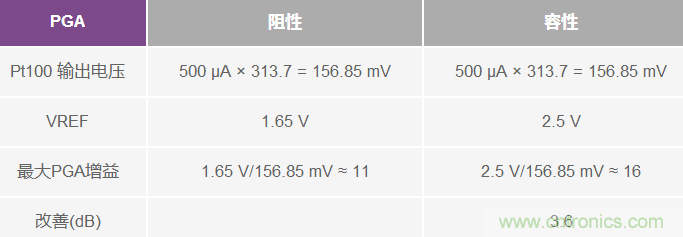

圖1顯示了不同采樣頻率下的量化噪聲密度示例����。

圖1.不同采樣頻率下,頻率范圍內(nèi)的量化噪聲密度�。

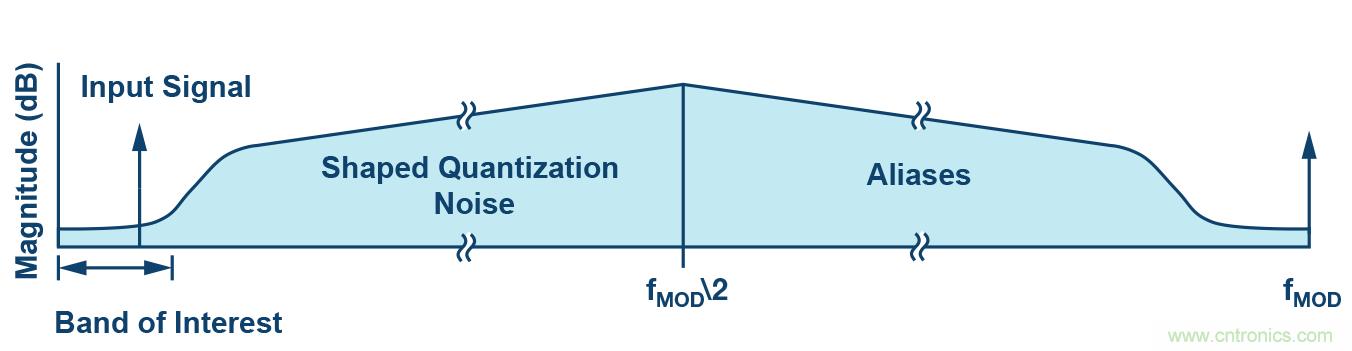

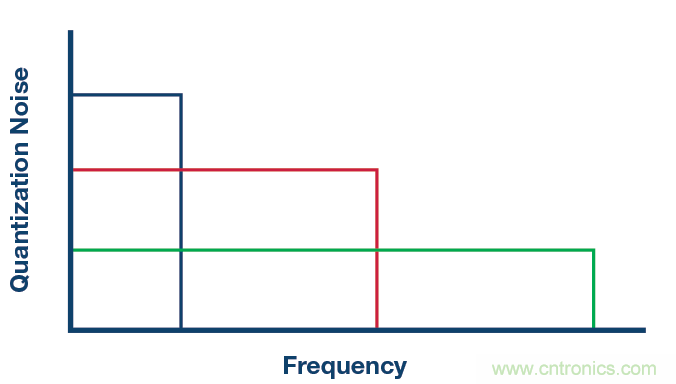

一般而言,對于特定的目標頻段��,每2個過采樣系數(shù)就會使動態(tài)范圍改善3dB(假定為白噪聲頻譜)�。Σ-Δ型轉(zhuǎn)換器的第二個優(yōu)勢是噪聲傳遞函數(shù)。它將噪聲整形至更高頻率(如圖2所示)��,進一步降低了目標頻段內(nèi)的量化噪聲���。

圖2.Σ-Δ噪聲整形

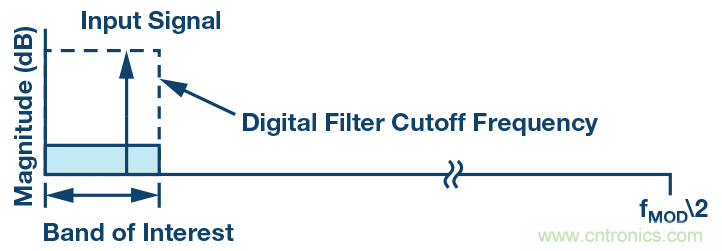

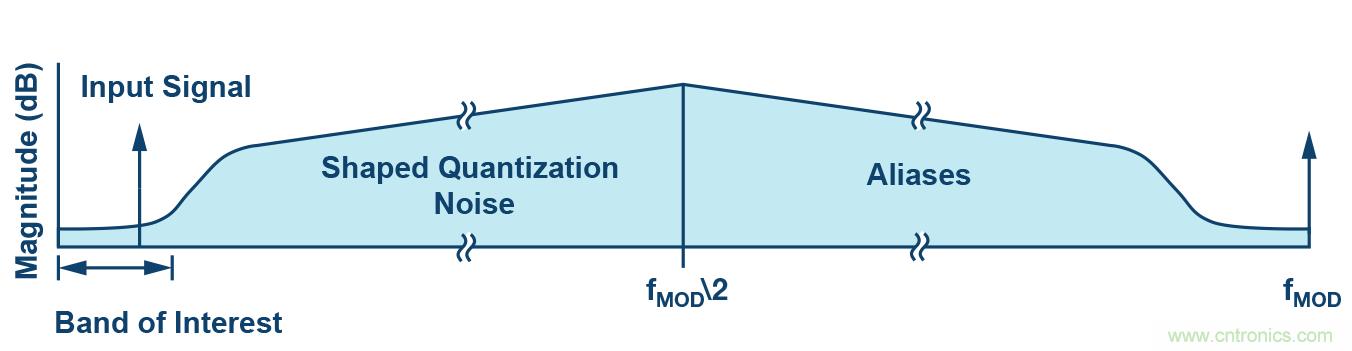

此外���,Σ-Δ架構(gòu)可能集成數(shù)字濾波器,用來移除目標頻段外的量化噪聲���,實現(xiàn)出色的動態(tài)范圍性能�,如圖3所示。

圖3.LPF之后的量化噪聲�����。

過采樣架構(gòu)的缺點之一是��,相比其它采樣頻率較低的架構(gòu)��,驅(qū)動Σ-Δ型調(diào)制器的輸入緩沖器要求可能會更嚴格��。采集時間變得更短�,因此緩沖器需要更高帶寬?,F(xiàn)代Σ-Δ型轉(zhuǎn)換器片上集成輸入緩沖器,最大程度簡化使用

此外�,在檢測系統(tǒng)中,為檢測元件提供具有高精度的極高輸入阻抗對于測量精度而言極為關(guān)鍵��。這使得輸入緩沖器的要求更為嚴格了����。

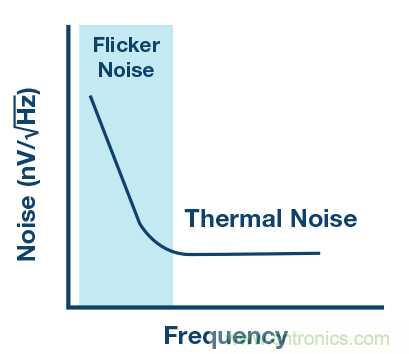

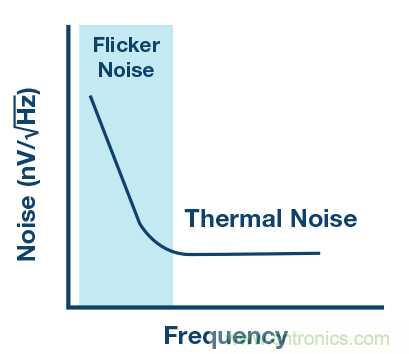

集成輸入緩沖器還有其它挑戰(zhàn)。Σ-Δ型調(diào)制器可在低頻率時提供極低噪聲�,但所有其它元件(比如輸入緩沖器)都會使熱噪聲增加,而更嚴重的則是低頻閃爍噪聲����,如圖4所示����。

圖4.閃爍噪聲����。

此外,緩沖器失調(diào)也可能增加總系統(tǒng)誤差��。通過系統(tǒng)校準可以補償失調(diào)����,但如果失調(diào)漂移相對較高,那么這種方式就無法實現(xiàn)�����,因為每次工作溫度發(fā)生改變都會要求系統(tǒng)重新校準����,以補償緩沖器失調(diào)。

例如���,當失調(diào)漂移為500 nV/°C時�����,10°C溫度遞增將等于5 μV失調(diào)范圍����,在±2.5 VREF 24位ADC中這相當于16.8 LSB,即約為4位�����。

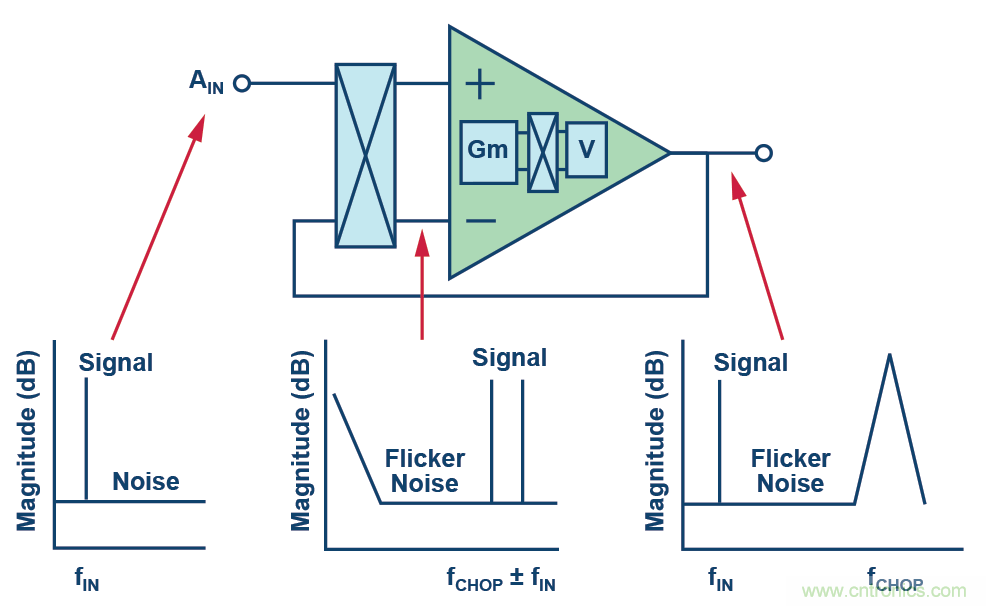

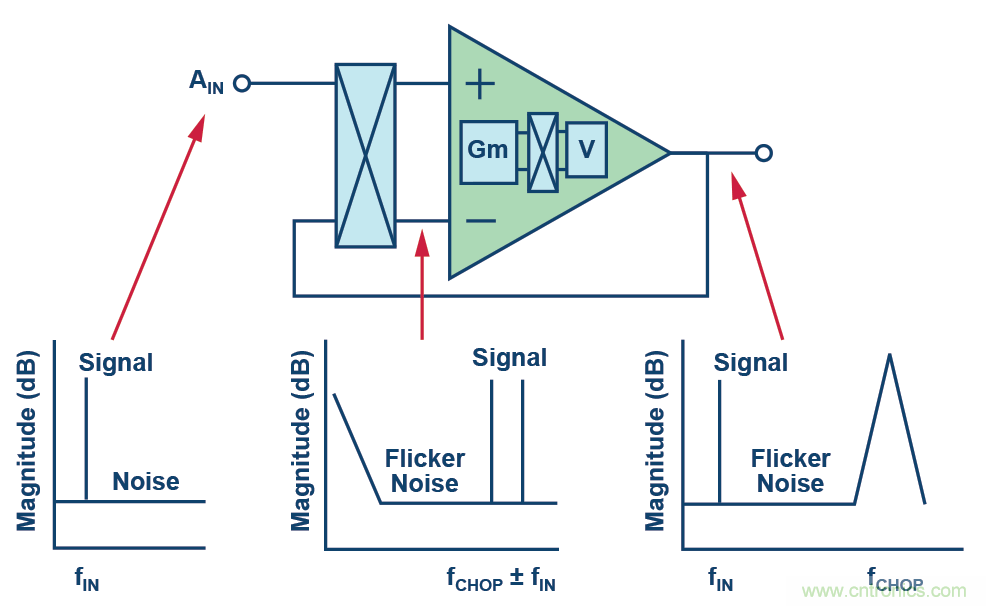

解決這兩個問題的典型途徑是對緩沖器的輸入和輸出進行斬波��,如圖5所示����。

圖5.斬波放大器���。

對輸入進行斬波之后�,輸入頻率便調(diào)制到較高頻率����。緩沖器失調(diào)和閃爍噪聲依然保持其最初的低頻率,因為它們不受輸入斬波的影響�����。

輸出去斬波機制將輸入頻率解調(diào)回基帶,同時向上調(diào)制緩沖器產(chǎn)生的失調(diào)和閃爍噪聲至較高頻率�,隨后由ADC低通濾波器加以消除。

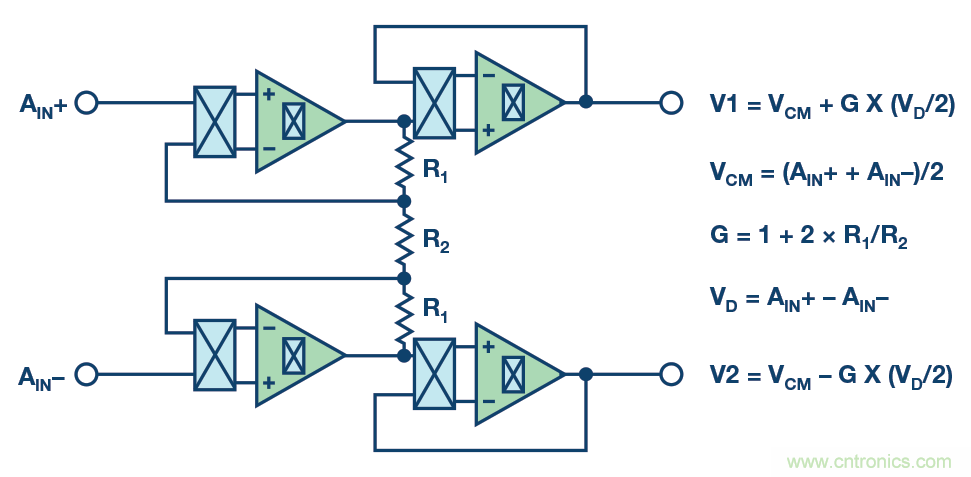

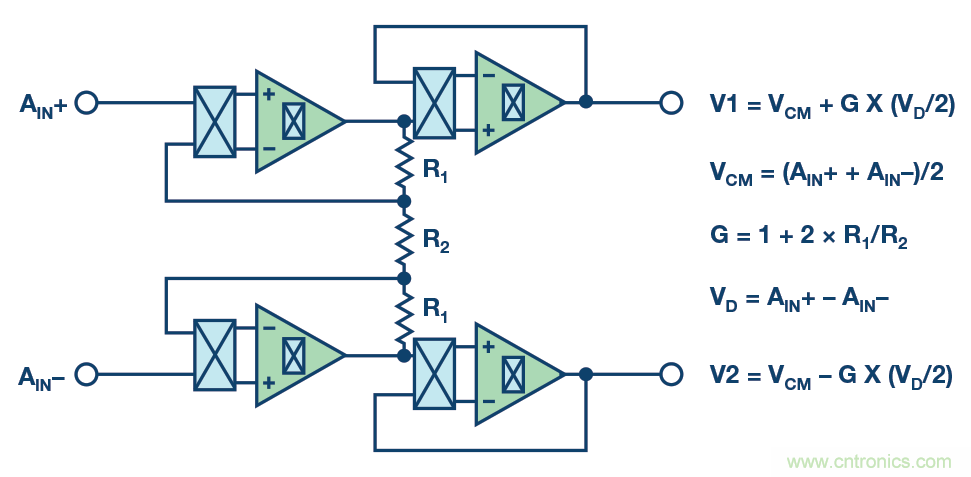

某些情況下����,輸入緩沖器可以采用基于電阻的儀表放大器(阻性PGA)來代替,以使小傳感器信號滿足全調(diào)制器輸入范圍���,最大程度提升動態(tài)范圍�����。需注意��,基于電阻的儀表放大器相比差分阻性放大器是更好的選擇�����,因為分立式傳感器需要更高的輸入阻抗�。阻性PGA可實現(xiàn)類似的斬波方案��,如圖6所示。

圖6.阻性PGA���。

阻性PGA可能需要級聯(lián)第二組緩沖器��,因為放大器可能無法提供直接驅(qū)動調(diào)制器所需要的足夠帶寬�����。同時�,必須保持低功耗���,這就確定了電阻值���,進而確定了放大器帶寬。

使用這種放大器拓撲的主要問題是��,它限制了共模電壓——尤其是在增益大于1的時候��,因為阻性PGA具有取決于輸入信號的浮動共模值����,如圖6所示��。

此外,阻性網(wǎng)絡(luò)失配及其漂移也是影響總誤差預(yù)算的因素之一����,因為它可能會影響大多數(shù)的精度規(guī)格。

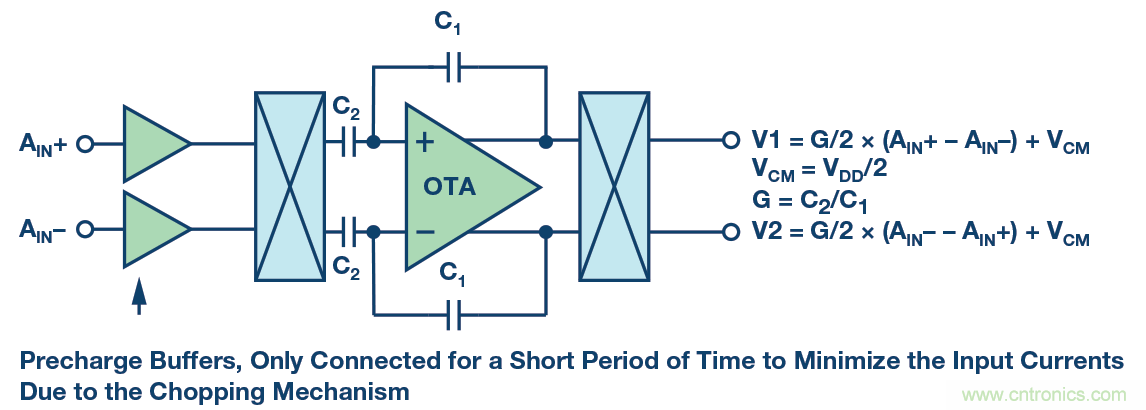

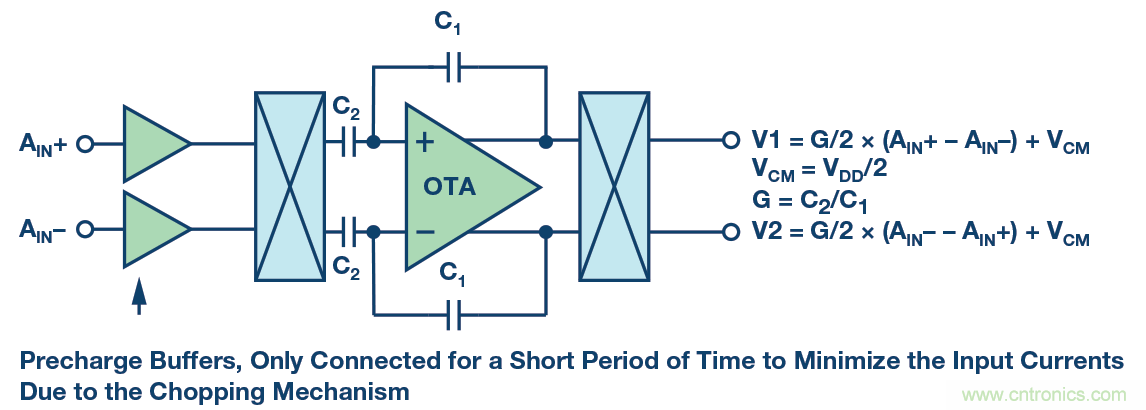

為避免這些限制����,最新的Σ-Δ型轉(zhuǎn)換器采用了容性PGA。

容性PGA放大原理與阻性PGA相似:增益取決于電容比��,如圖7所示����。

圖7.容性PGA(為簡便起見,移除了部分模塊)���。

為了放大直流信號����,容性PGA在PGA輸入端引入了斬波機制直流輸入信號調(diào)制到斬波頻率����,然后由容性放大器進行放大。最后����,信號通過輸出去斬波解調(diào)回直流��。此外���,放大器失調(diào)和閃爍噪聲調(diào)制到斬波頻率,并在之后的級中進行低通濾波��。

相比阻性架構(gòu)�,這種容性架構(gòu)有一些優(yōu)勢:

它能更好地權(quán)衡噪聲與功率,因為噪聲源較少��。需要較少的放大器�����,而且相比電阻�,電容不會產(chǎn)生噪聲。

電容比電阻有非常多的優(yōu)勢�����。除了無噪聲外���,電容不會受到自發(fā)熱影響����,且通常具有更好的匹配和溫度漂移��。這對失調(diào)��、增益誤差和漂移規(guī)格有正面影響�����。

電容可將輸入共模從信號鏈共模的其余部分去耦����。這樣可以提供CMRR、PSRR和THD等優(yōu)勢�����。

容性PGA的最大優(yōu)勢之一�,是它的輸入共模范圍可以是軌到軌或更高。這樣便有可能從正供電軌下至負供電軌的幾乎任何地方對傳感器共模電壓進行偏置�。

這種容性架構(gòu)結(jié)合了儀表放大器的優(yōu)勢,具有極高的輸入阻抗(因為輸入阻抗是一個電容)�,其優(yōu)勢是電容(而不是電阻)作為增益元件,增加了放大器的動態(tài)范圍——這不僅是因為它的信號擺幅����,還因為其噪聲效率的緣故����。

克服阻性PGA共模限制的常見解決方案是增加或偏移供電軌���,或者重新對中傳感器信號共模��。這樣做的代價是功耗更高��、電源設(shè)計更復(fù)雜����、使用更多外部元件���,以及更高的成本����。

實際例子

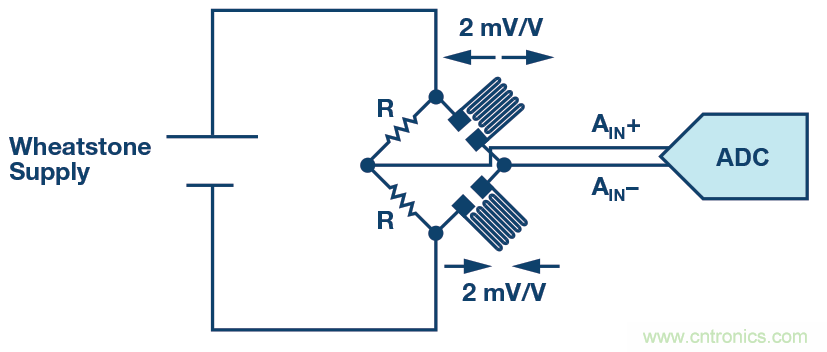

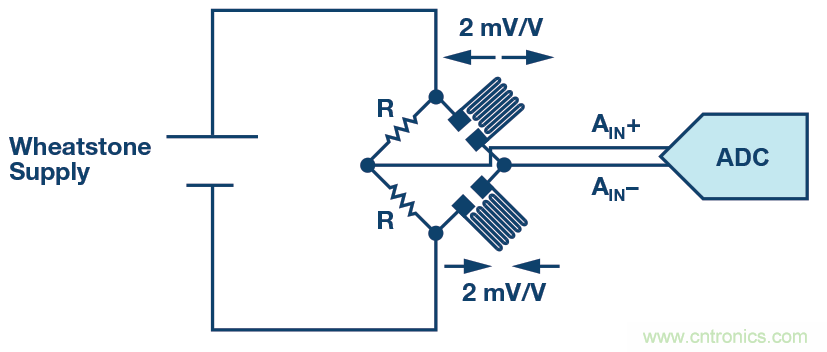

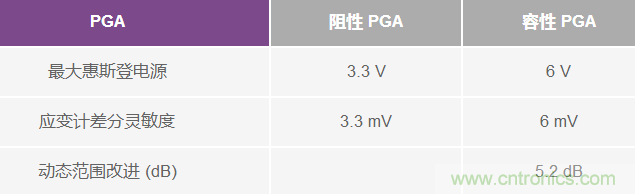

在惠斯登電橋中�����,共模電壓由連接兩個橋臂的阻抗決定����,且與施加的電源成正比���。電子秤應(yīng)用即采用這種檢測拓撲����,因為它具有針對應(yīng)變計的線性檢測優(yōu)勢;圖8顯示了一個半橋式II類電路���。

圖8.采用惠斯登拓撲并包含應(yīng)變計的電子秤��。

應(yīng)變計的靈敏度通常為2mV/V��?���;菟沟请娫丛礁?���,靈敏度也就越高。為了增加應(yīng)變計的動態(tài)范圍并最大化SNR��,電橋可能采用比ADC更高的電源供電���。

由于阻性PGA的共模限制���,電橋應(yīng)當采用與ADC相同的電源供電����,以便最大程度提升動態(tài)范圍��;而在容性PGA中����,電橋可以采用幾乎為ADC兩倍的電源供電,因為不存在輸入共模的限制�����。

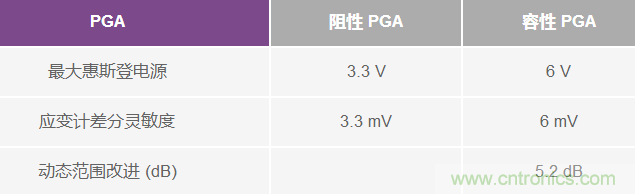

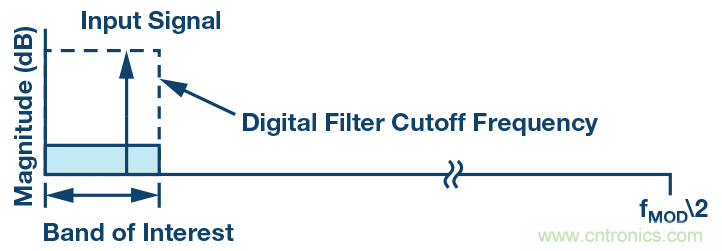

例如���,假設(shè)標準電源為ADC提供3.3V電平��,則對于相同的增益�,容性PGA相比阻性PGA的改進總結(jié)見表1�����。

表1. 惠斯登電橋中的阻性PGA和容性PGA對比(假設(shè)使用標準電源和增益)

可能存在的另一個問題,是當電橋的連接位置離ADC較遠時�����,接地之間可能有所不同���。這也許會使共模電壓偏移�,從而導(dǎo)致ADC輸入共模相對于電橋不平衡���,并降低阻性PGA中的最大允許增益。

使容性PGA性能與阻性PGA相當?shù)目尚修k法是以更高的電源電壓對電橋供電�����。比如���,以±3.3 V雙極性電源對電橋供電�,從而增加應(yīng)變計的靈敏度�,但代價是更高的系統(tǒng)復(fù)雜性和功耗。

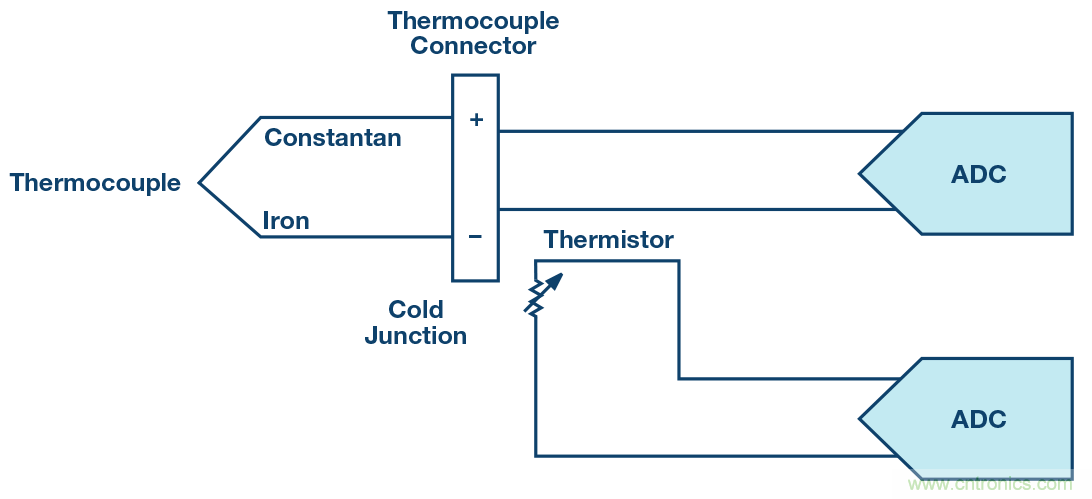

可能會得益于容性PGA的另一個例子是采用電阻式溫度檢測器(RTD)或熱電偶的溫度測量應(yīng)用��。

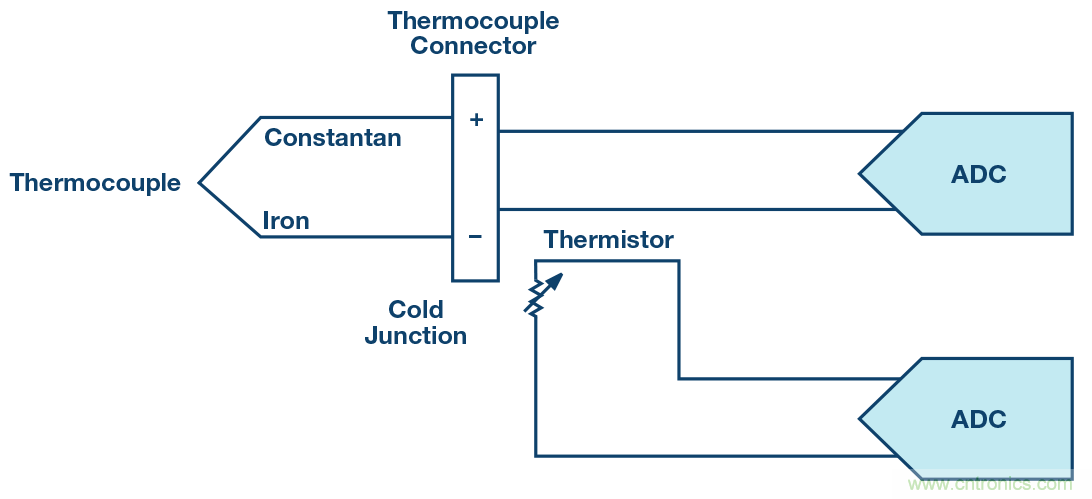

常用RTD電阻(比如PT100)可以用來直接檢測溫度�����,或間接檢測熱電偶的冷結(jié),如圖9所示��。

圖9.典型熱電偶設(shè)置�。

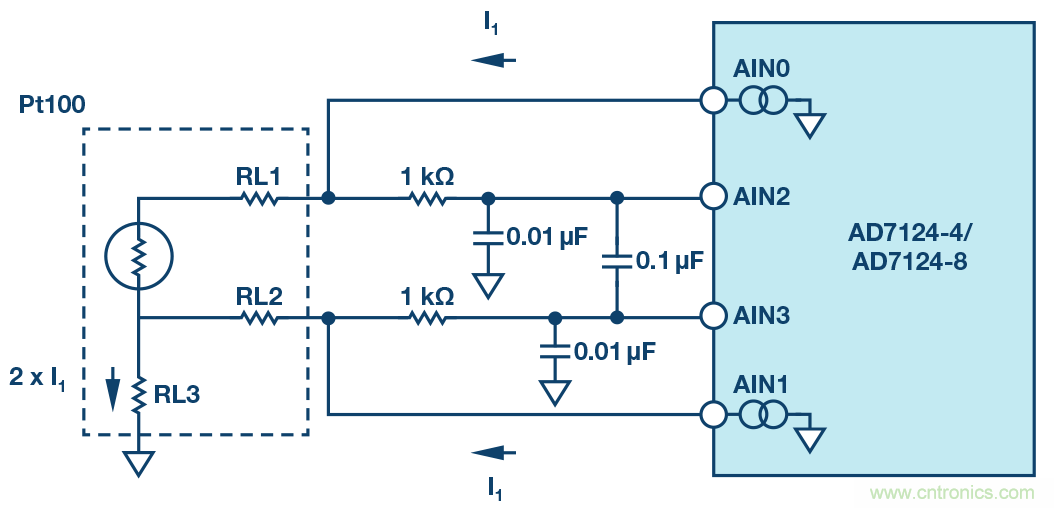

每一個PT100器件都提供不同的導(dǎo)線,采用最受歡迎的高性價比三線式配置����。

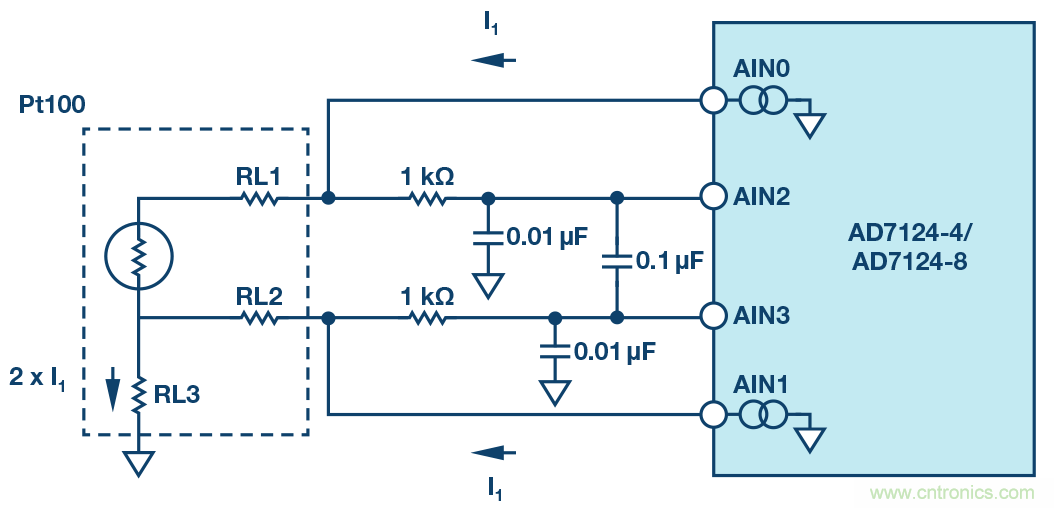

測量溫度并消除引線誤差的傳統(tǒng)方法如圖10所示。本例中��,集成PGA的Σ-Δ型ADCAD7124-8的內(nèi)部電流源以相同電流驅(qū)動雙線式RTD���,在兩個引線上產(chǎn)生相同的失調(diào)誤差����,其值與引線電阻成正比���。

由于 AD7174-8 具有較小的引線電阻和電流(為了最大程度減少自發(fā)熱效應(yīng))����,RL3產(chǎn)生的失調(diào)電壓靠近負供電軌,極大地降低了阻性PGA中允許的最大增益����,因為其輸入共模相比容性PGA同樣將會非常接近供電軌,在內(nèi)部將共模電壓設(shè)為電源供電軌的一半�����,允許更高的增益配置���,從而提高總動態(tài)范圍�。

建議的解決方案極大降低了系統(tǒng)和硬件連接的復(fù)雜性��,因為第三條線纜不應(yīng)返回至ADC PCB�,并可連接RTD位置附近的地��。

圖10.三線式RTD測量����。

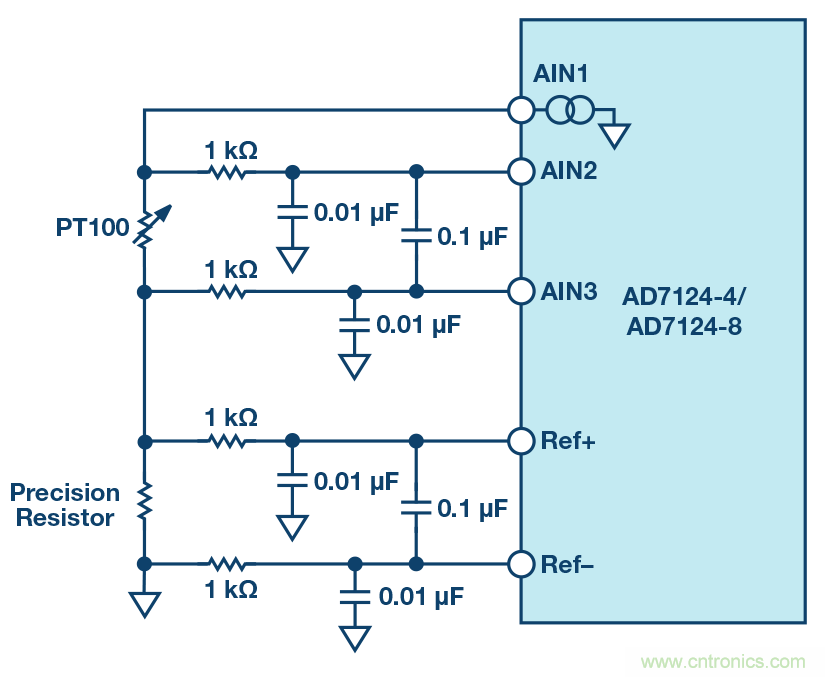

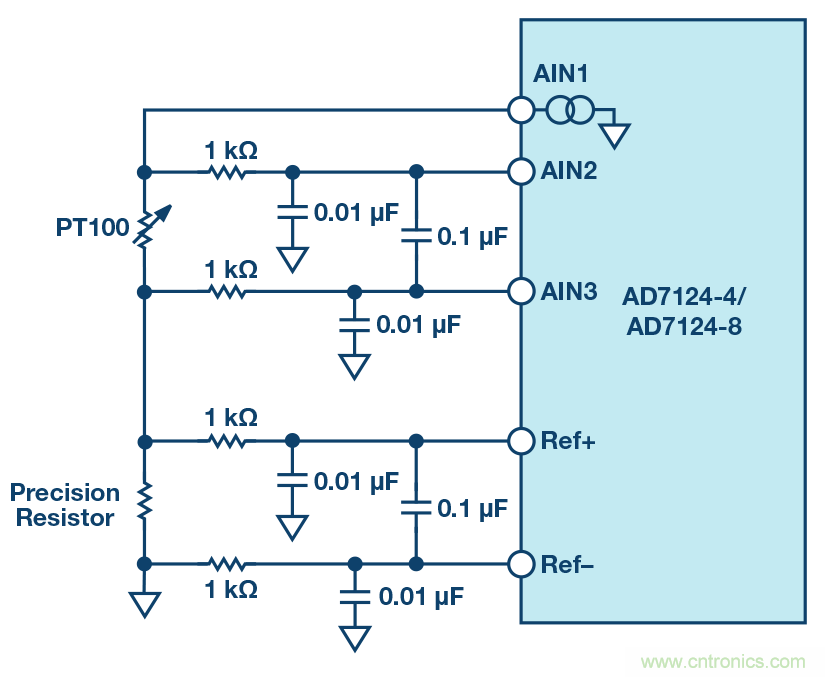

為了增加溫度測量的精度,建議采用四線式測量���。本例中��,只使用了一個電流基準���。為了避免電流源的不精確性�����,可以將精密電阻用作ADC基準電壓發(fā)生器來進行比例測量�,如圖11所示���。

圖11 .比例四線式RTD測量�。

選擇適當?shù)耐獠烤茈娮柚?,使RTD上產(chǎn)生的最大電壓等于基準電壓除以PGA增益。

對于3.3 V電源而言����,在阻性PGA中,精密電阻上產(chǎn)生的電壓應(yīng)為1.65 V左右���,否則PGA共模電壓將限制最大增益����。其結(jié)果是�,最大增益信號應(yīng)等于1.65V���。在容性PGA中,不存在輸入共模的限制��,因此RTD共模信號可以靠近頂部供電軌放置���,最大程度提升了精密電阻生成的ADC基準電壓�,并因此實現(xiàn)最高的可選增益和動態(tài)范圍�。

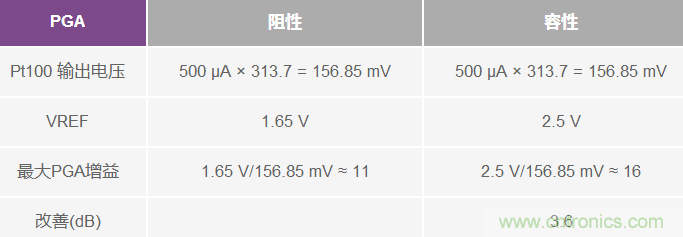

表2總結(jié)了阻性PGA相對于容性PGA的最大增益,最大電流源為500μA��,限制了Pt100的自發(fā)熱(假定B類RTD����,此時最高溫度為600°C,最大VREF為2.5 V)�����。

表2. 四線式RTD比例測量中的阻性和容性PGA對比

結(jié)論

相比阻性PGA�����,容性PGA具有多項重要優(yōu)勢�。諸如噪聲、共模抑制���、失調(diào)��、增益誤差以及溫度漂移等關(guān)鍵規(guī)格都由于電容作為增益元件的固有溫度穩(wěn)定性以及匹配屬性而得到了改善���。

另一項重要特性是內(nèi)部共模電壓從放大器內(nèi)部共模電壓中去耦。當待放大的輸入信號為靠近供電軌的共模電壓時�,這點尤為重要。阻性PGA的增益選擇嚴重受限于其共模限制�����,或者要求更高的供電軌或外部元件將輸入信號重新偏置到供電軌的一半�����。而容性PGA卻可以輕松處理這種檢測場景���。

推薦閱讀: