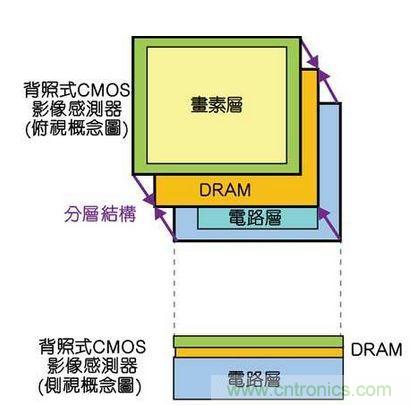

【導(dǎo)讀】為了加速影像數(shù)據(jù)處理, 業(yè)界研發(fā)了在互補金屬氧化物半導(dǎo)體(CMOS)影像傳感器中配備嵌入式動態(tài)隨機存取存儲器(DRAM),推出了配備DRAM的三層堆疊式CMOS影像傳感器,SONY是最早發(fā)布這一產(chǎn)品的廠家,這款型號為IMX400的三層堆疊式感光元件(Exmor RS)是專為智能手機而打造的。

SONY的堆疊式CMOS傳感器元件

Sony的Xperia XZ Premium和Xperia XZ兩款旗艦級智能手機搭載了具有960fps畫面更新率的Motion Eye相機模組。

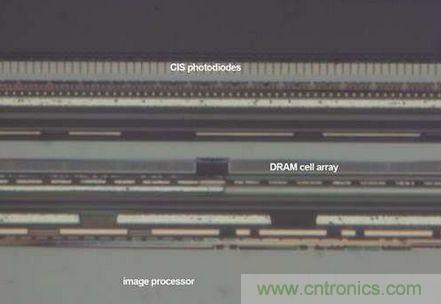

這款三層堆疊的CMOS影像傳感器(CIS)被面對背地安裝在DRAM上,使得DRAM與影像訊號處理器(ISP)面對面接在一起。

Sony三層堆疊式CMOS影像傳感器的芯片橫截面

Sony在其較早的19Mp影像傳感器中使用雙模擬/數(shù)位轉(zhuǎn)換器(ADC),為畫素資料進行數(shù)字化。而今,該公司使用4層ADC的結(jié)構(gòu)提高讀取速度,同時也改善了處理能力。DRAM則用于暫時儲存高速數(shù)據(jù),然后再以傳感器介面的最佳速率輸出。該設(shè)計使其能以1/120秒讀取1,930萬畫素的靜態(tài)影像,而在影片模式下可達到1,000fps的畫面更新率,較以往產(chǎn)品的靜態(tài)影像與動態(tài)影片分別提高了4倍和8倍的速度。Sony可說是再次將手機相機的功能推至極限。

Sony新開發(fā)配備DRAM的三層堆疊式CMOS影像傳感器

3D堆疊技術(shù)

3D 堆疊技術(shù)是把不同功能的芯片或結(jié)構(gòu), 通過堆疊技術(shù)和過孔互連等微機械加工技術(shù), 使其在 Z軸方向上形成立體集成和信號連通以及圓片級、芯片級、硅帽封裝等封裝和可靠性技術(shù)為目標(biāo)的三維立體堆疊加工技術(shù), 用于微系統(tǒng)集成, 是繼片上系統(tǒng)( SOC) 、多芯片模塊( MCM ) 之后發(fā)展起來的系統(tǒng)級封裝( SiP/ SoP) 的先進制造新技術(shù)。

微電子的模塊已經(jīng)實現(xiàn) 3D 圓片級封裝( WLP)的 系統(tǒng)級封 裝 ( SiP ) 技術(shù), 例如, CIS RF 模塊、M EM S 封裝、標(biāo)準(zhǔn)器件封裝, 已有量產(chǎn), 2009 年開始 3D TSV 堆疊時代( 3D TSV Stack Era ) 的到來,模塊化芯片、閃存及 DRAM , 通過堆疊以獲得增強的內(nèi)存容量。

3D 堆疊的主要形式和分類

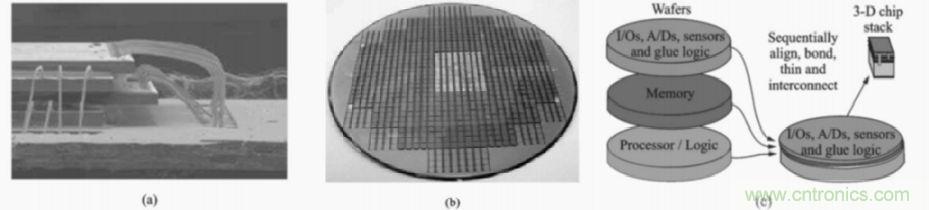

目前有多種基于 3D 堆疊方法, 主要包括: 芯片與芯片的堆疊( D2D) 、芯片與圓片的堆疊( D2W ) 以及圓片與圓片的堆疊( W2W) 。

D2D 堆疊方式是當(dāng)前系統(tǒng)級封裝( SiP) 方式的主要互聯(lián)方式, 該堆疊方法主要利用引線鍵合的方式, 實現(xiàn)3D 方向芯片間的互聯(lián), 如圖( a) 所示。 D2D 方式雖然可以實現(xiàn)3D 堆疊, 提高系統(tǒng)集成度, 但由于主要使用引線鍵合方式互聯(lián), 限制了系統(tǒng)集成度進一步提高, 并由于引線會引入寄生效應(yīng), 降低了 3D 系統(tǒng)的性能;

D2W 堆疊方式利用芯片分別與圓片相應(yīng)功能位置實現(xiàn)3D 堆疊,如圖( b) 所示, 該種方式主要利用 flip-chip( 倒裝)方式和bump( 置球) 鍵合方式, 實現(xiàn)芯片與圓片電極的互聯(lián), 該方式與 D2D 方式相比, 具有更高的互聯(lián)密度和性能, 并且與高性能的 flip-chip 鍵合機配合,可以獲得較高的生產(chǎn)效率;

W2W 堆疊方式利用圓片與圓片鍵合, 實現(xiàn)3D 堆疊, 在圓片鍵合過程中, 利用 TSV 實現(xiàn)信號的互聯(lián), 如圖( c) 所示, 該種方式具有互聯(lián)密度高、成本低并且可同時實現(xiàn)圓片級封裝( WLP) 的優(yōu)點, 可以實現(xiàn) AD、I/ O、傳感器等多功能器件的混合集成。

對于 D2W 和 W2W 堆疊方式,從生產(chǎn)效率的角度, W 2W 方式效率最高, 但從成品率角度考慮, 由于 D2W 方式可以通過篩選, 實現(xiàn)合格芯片( Know good die, KGD) 之間的堆疊, 因此成品率較高; 而 W2W 方式, 無法通過實現(xiàn)事先篩選,

會嚴(yán)重影響堆疊的成品率。

對于 W2W 堆疊方式, 必須嚴(yán)格控制芯片及 3D 堆疊工藝的成品率, 否則, 隨著堆疊層數(shù)的增加, 成品率將大幅下降。 對于一個需要 3 層的堆疊工藝來說, 必須將圓片成品率及層疊成品率均控制在 98%以上, 才可能獲得 90%以上的 3D 堆疊成品率。

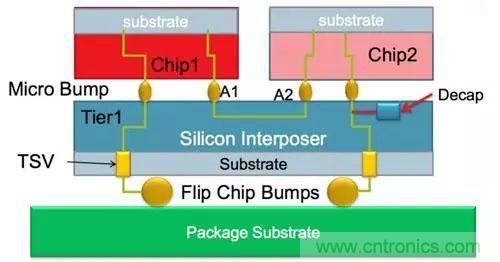

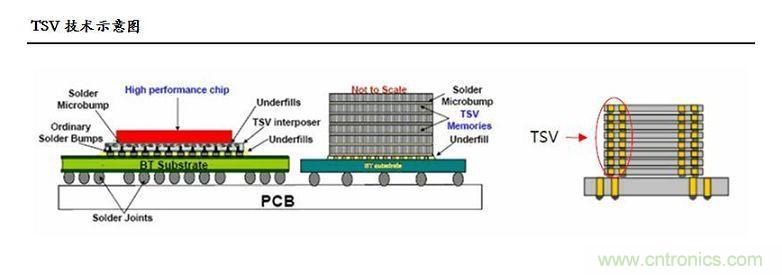

層間互聯(lián)技術(shù)——TSV

從微電子技術(shù)的發(fā)展趨勢看, 基于 TSV 技術(shù)的3D 堆疊技術(shù), 將是微電子技術(shù)發(fā)展的必然趨勢, 但也面臨許多技術(shù)挑戰(zhàn), 如 TSV 技術(shù)、超薄片加工技術(shù)( 臨時鍵合、減薄等) 、異質(zhì)鍵合技術(shù)、層間對準(zhǔn)技術(shù)等等, 其中, TSV 技術(shù)最為關(guān)鍵。

穿透硅通孔( TSV) 將在先進的三維集成電路( 3D IC) 設(shè)計中提供多層芯片之間的互連功能, 是通過在芯片和芯片之間、晶圓和晶圓之間制作垂直導(dǎo)通, 實現(xiàn)芯片之間互連的最新技術(shù)。 與以往的IC 封裝鍵合和使用凸點的疊加技術(shù)不同, TSV 能夠使芯片在三維方向堆疊的密度最大、外形尺寸最小, 并且大大改善芯片速度和降低功耗的性能。

采用硅通孔技術(shù)( TSVs) 的堆疊器件

TSV 與目前應(yīng)用于多層互連的通孔有所不同,一方面 TSV 通孔的直徑通常僅為為 1~100 μm , 深度 10~400 μm, 為集成電路或者其他多功能器件的高密度混合集成提供可能; 另一方面, 它們不僅需要穿透組成疊層電路的各種材料, 還需要穿透很厚的硅襯底, 因此對通孔的刻蝕技術(shù)具有較高的要求。目前制造商們正在考慮的多種三維集成方案, 也需要多種尺寸的T SV 與之配合。 等離子刻蝕技術(shù)已經(jīng)廣泛應(yīng)用于存儲器和 MEM S 生產(chǎn)的深硅刻蝕工藝, 同樣也非常適合于制造 TSV。

利用3D 堆疊技術(shù)實現(xiàn)微系統(tǒng), 是未來發(fā)展的必然趨勢, 是突破摩爾定律發(fā)展的必然選擇。其中利用MEMS 技術(shù)實現(xiàn) TSV 互連, 是該技術(shù)的核心技術(shù),必須重點解決與突破。

本文轉(zhuǎn)載自傳感器技術(shù)。

推薦閱讀: