【導(dǎo)讀】時(shí)鐘接口閾值區(qū)間附近的抖動(dòng)會(huì)破壞ADC的時(shí)序��。例如���,抖動(dòng)會(huì)導(dǎo)致ADC在錯(cuò)誤的時(shí)間采樣,造成對(duì)模擬輸入的誤采樣���,并且降低器件的信噪比(SNR)��。降低抖動(dòng)有很多不同的方法����,但是�,在get降低抖動(dòng)的方法前我們必須找到抖動(dòng)的根本原因!

時(shí)鐘抖動(dòng)����,why?

時(shí)鐘抖動(dòng)的根本原因就是時(shí)鐘和ADC之間的電路噪聲。隨機(jī)抖動(dòng)由隨機(jī)噪聲引起�����,主要隨機(jī)噪聲源包括

● 熱噪聲(約翰遜或奈奎斯特噪聲)�,由載流子的布朗運(yùn)動(dòng)引起。

● 散粒噪聲����,與流經(jīng)勢(shì)壘的直流電流有關(guān)�,該勢(shì)壘不連續(xù)平滑,由載流子的單獨(dú)流動(dòng)引起的電流脈沖所造成�。

● 閃爍噪聲�����,出現(xiàn)在直流電流流動(dòng)時(shí)�����。該噪聲由攜帶載流子的半導(dǎo)體中的陷阱引起�����,這些載流子在釋放前通常會(huì)形成持續(xù)時(shí)間較短的直流電流。

● 爆裂噪聲���,也稱爆米花噪聲,由硅表面的污染或晶格錯(cuò)位造成�����,會(huì)隨機(jī)采集或釋放載流子���。

ps.以上噪聲我們?cè)鴮⒃敿?xì)講解過(guò)��,有興趣的筒子點(diǎn)擊藍(lán)色字體查看~

查看時(shí)鐘信號(hào)噪聲�,how���?

確定性抖動(dòng)由干擾引起�����,會(huì)通過(guò)某些方式使閾值發(fā)生偏移���,通常受器件本身特性限制�。查看時(shí)鐘信號(hào)噪聲通常有三種途徑:時(shí)域����、頻域、相位域�。

咳咳,敲黑板劃重點(diǎn)�����,以上三種途徑的具體方法如下↓↓↓

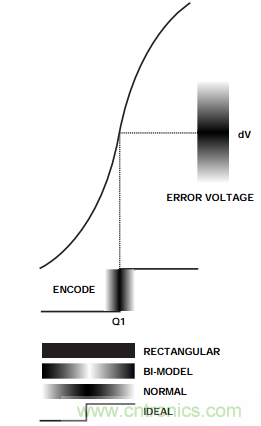

時(shí)域圖

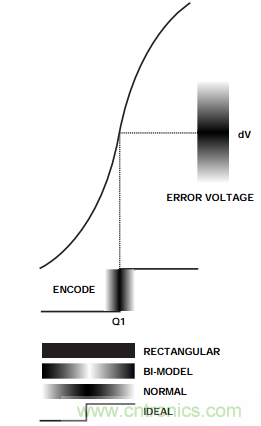

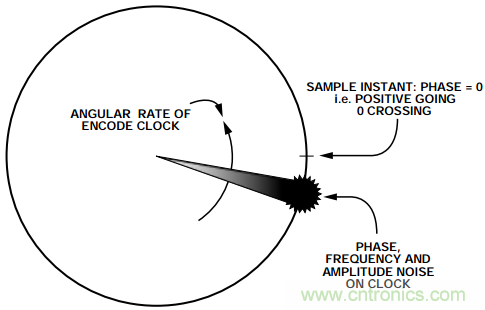

圖1. 抖動(dòng)的時(shí)域圖

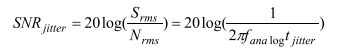

時(shí)鐘抖動(dòng)是編碼時(shí)鐘的樣本(不同周期)間的變化����,包括外部和內(nèi)部抖動(dòng)。抖動(dòng)引起的滿量程信噪比由以下公式得出

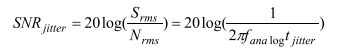

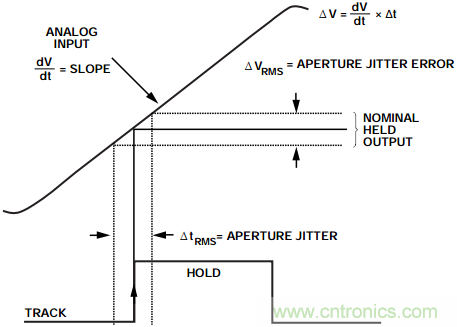

舉個(gè)栗子�,頻率為1 Ghz,抖動(dòng)為100 FS均方根值時(shí)����,信噪比為64 dB。在時(shí)域中查看時(shí)���,x軸方向的編碼邊沿變化會(huì)導(dǎo)致y軸誤差�,幅度取決于邊沿的上升時(shí)間?����?讖蕉秳?dòng)會(huì)在ADC輸出產(chǎn)生誤差�,如圖2所示。抖動(dòng)可能產(chǎn)生于內(nèi)部的ADC����、外部的采樣時(shí)鐘或接口電路���。

圖2. 孔徑抖動(dòng)和采樣時(shí)鐘抖動(dòng)的影響

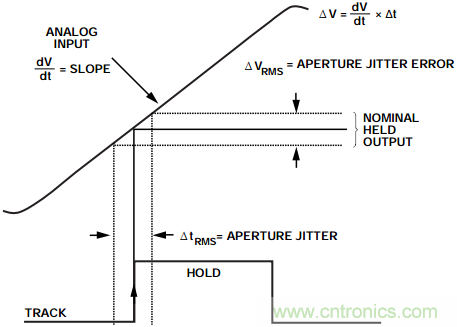

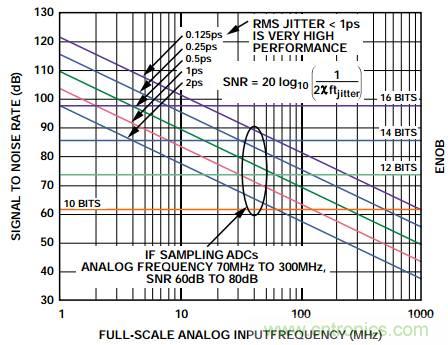

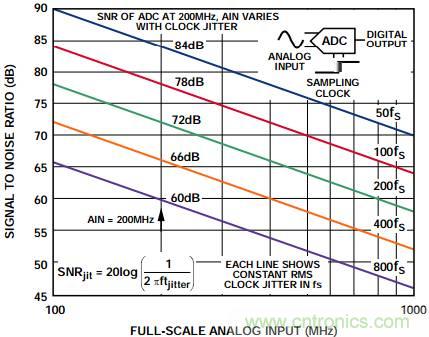

圖3顯示抖動(dòng)對(duì)信噪比的影響����。圖中顯示了5條線�,分別代表不同的抖動(dòng)值。x軸是滿量程模擬輸入頻率��,y軸是由抖動(dòng)引起的信噪比����,有別于ADC總信噪比���。

圖3. 時(shí)鐘抖動(dòng)隨模擬信號(hào)增大而提升信噪比

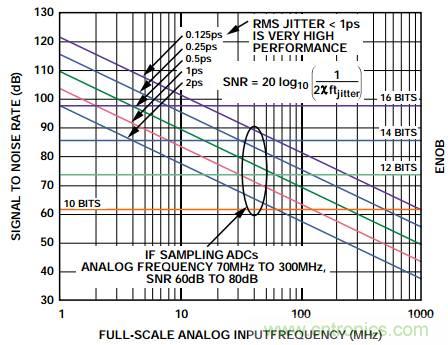

由抖動(dòng)引起的信噪比和有效位數(shù)(ENOB)的關(guān)系由以下公式定義:

SNR = 6.02 N + 1.76 dB

其中N =有效位數(shù)�。滿量程100 MHz輸入時(shí)��,14位有效位數(shù)要求均方根抖動(dòng)不超過(guò)0.125 ps或125 fs�����。該公式假定ADC具有無(wú)限分辨率�����,其中的唯一誤差是由時(shí)鐘抖動(dòng)產(chǎn)生的噪聲。

圖4. 由抖動(dòng)產(chǎn)生的理論信噪比和有效位數(shù)與滿量程正弦波模擬輸入頻率的關(guān)系

頻域圖

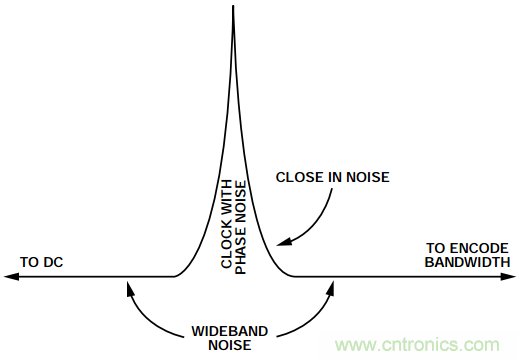

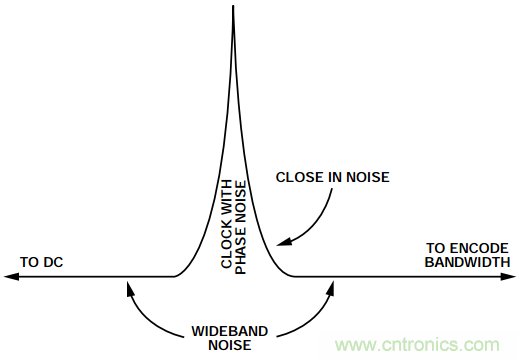

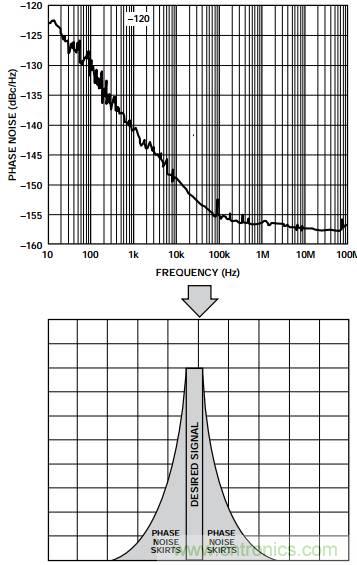

近載波噪聲出現(xiàn)在采樣時(shí)鐘中心頻率和等于信號(hào)帶寬一半的單邊帶(SSB)失調(diào)之間�����。寬帶噪聲的范圍從單邊帶失調(diào)到½時(shí)鐘接收器帶寬����。

圖5. 頻域圖

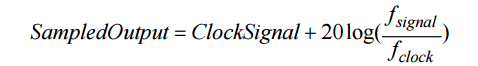

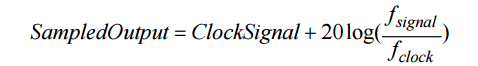

時(shí)間的乘法運(yùn)算是在頻域中進(jìn)行卷積。因此�����,時(shí)鐘上在頻域上的任何“裙邊”都會(huì)施加于數(shù)字信號(hào)�����。這會(huì)增加信號(hào)的EVM�����,降低整體性能���。卷積到采樣信號(hào)上的噪聲量取決于模擬頻率與采樣頻率的關(guān)系����。

圖6.卷積到采樣信號(hào)上的噪聲取決于模擬頻率和采樣頻率的關(guān)系

相位域圖

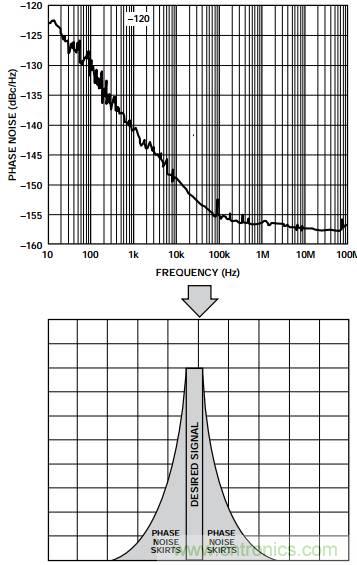

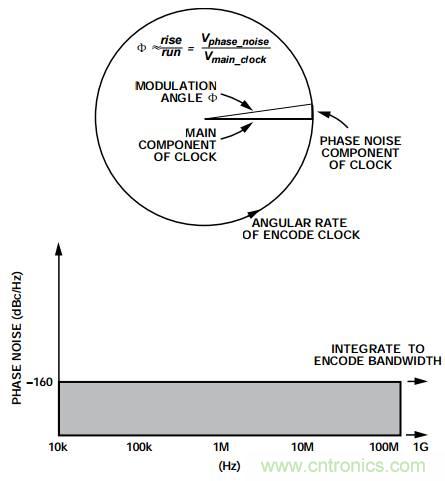

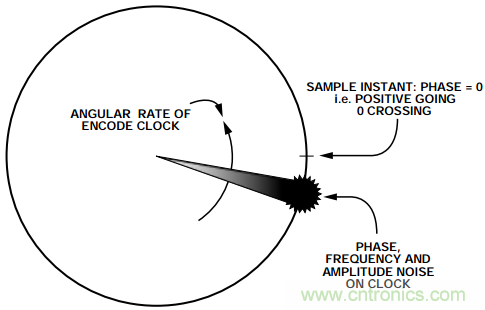

相位噪聲由每個(gè)時(shí)鐘周期之間的時(shí)間變化引起。最終結(jié)果是時(shí)鐘信號(hào)在基波頻率周圍變化�����,這一頻率范圍變化會(huì)降低ADC的信噪比����。

圖7.抖動(dòng)的相位域圖

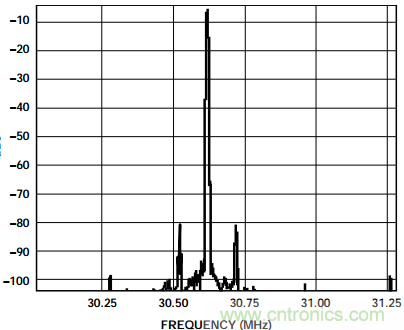

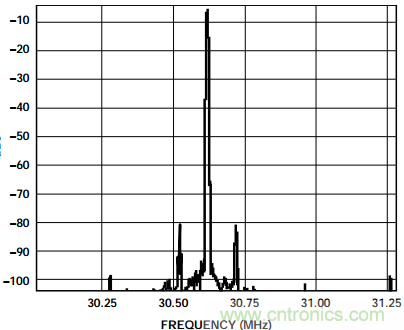

圖8所示的例子中�����,−66 dBc的雜散增加到78 MHz時(shí)鐘上����,用來(lái)將ADC采樣控制在30.62 MHz模擬信號(hào)。

圖8. 使用噪聲時(shí)鐘采樣時(shí)的30.62 MHz信號(hào)

雜散為−74.1 dBc���,按以下公式計(jì)算:

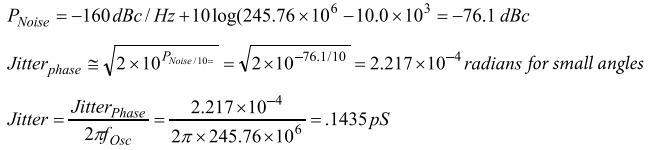

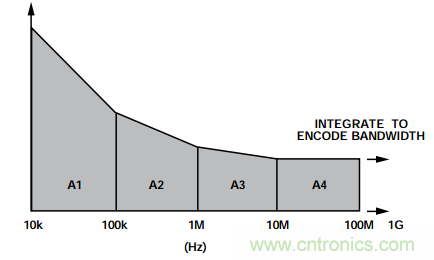

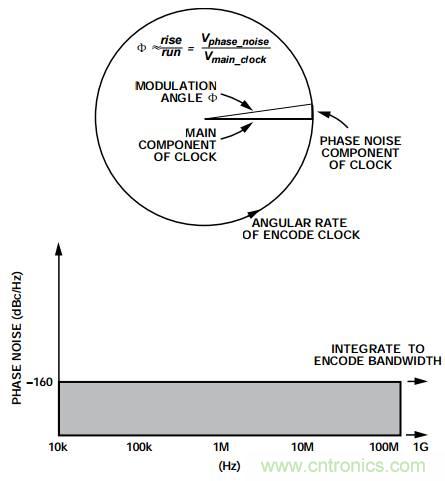

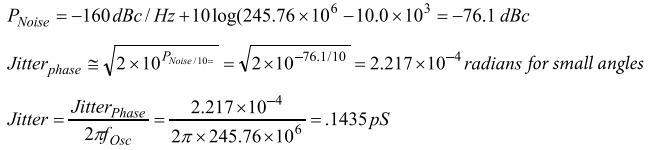

時(shí)鐘設(shè)計(jì)人員通常會(huì)提供一個(gè)相位噪聲�����,但不提供抖動(dòng)規(guī)格����。相位噪聲規(guī)格可以轉(zhuǎn)換為抖動(dòng),首先確定時(shí)鐘噪聲�����,然后通過(guò)小角度計(jì)算將噪聲與主時(shí)鐘噪聲成分進(jìn)行比較��。相位噪聲功率通過(guò)計(jì)算圖9中的灰色區(qū)域積分得出。

圖9. 對(duì)編碼帶寬的近載波到時(shí)鐘輸出噪聲進(jìn)行積分計(jì)算

高度為−160 dBc�����,寬度為10 KHz至245.76 MHz。因此���,

10×log(245.7e6 − 10e3)

= 83.9 dB�,−160 + 83.9 dB

= 76.1 dBc

得出積分噪聲��。

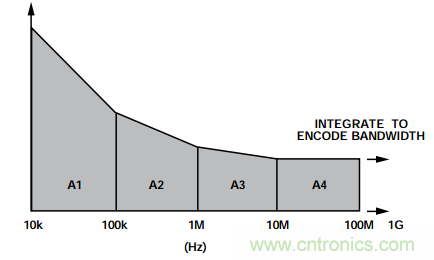

載波的失調(diào)不同����,噪聲的斜率也不同��。例如��,A1區(qū)域通常為1/f噪聲,而A4區(qū)域則視為寬帶噪聲��。

圖10.在頻率范圍內(nèi)的噪聲變化情況

A =面積=積分相位噪聲功率(dBc)抖動(dòng)可以通過(guò)對(duì)編碼帶寬的近載波到時(shí)鐘輸出的噪聲進(jìn)行積分計(jì)算確定���。頻率范圍應(yīng)分為較小的頻帶,然后相加得到總的結(jié)果:A = 10 log10 (A1 + A2 + A3 + A4)

本文轉(zhuǎn)載自ADI.

推薦閱讀: