【導讀】ROHM最近推出了SiC MOSFET的新系列產(chǎn)品“SCT3xxx xR系列”。SCT3xxx xR系列采用最新的溝槽柵極結構,進一步降低了導通電阻;同時通過采用單獨設置柵極驅動器用源極引腳的4引腳封裝,改善了開關特性,使開關損耗可以降低35%左右。此次,針對SiC MOSFET采用4引腳封裝的原因及其效果等議題,我們采訪了ROHM株式會社的應用工程師。

-關于SiC MOSFET的SCT3xxx xR系列,除了導通電阻很低,還通過采用4引腳封裝使開關損耗降低了35%,對此我們非常感興趣。此次,想請您以4引腳封裝為重點介紹一下該產(chǎn)品。

-首先,請您大致講一下4引腳封裝具體是怎樣的封裝,采用這種封裝的背景和目的是什么。

首先,采用4引腳封裝是為了改善SiC MOSFET的開關損耗。包括SiC MOSFET在內的電源開關用MOSFET和IGBT,被作為開關元件廣泛應用于各種電源應用和電源線路中。必須盡可能地降低這種開關元件產(chǎn)生的開關損耗和傳導損耗,但不同的應用,其降低損耗的方法也不盡相同。作為其中的一種手法,近年來發(fā)布了一種4引腳的新型封裝,即在MOSFET的源極、漏極、柵極三個引腳之外,另外設置了驅動器源極引腳。此次的SCT3xxx xR系列,旨在通過采用最新的溝槽柵極結構,實現(xiàn)更低的導通電阻和傳導損耗;通過采用4引腳封裝,進一步發(fā)揮出SiC本身具有的高速開關性能,并降低開關損耗。

-那么,我想詳細了解一下剛剛您的概述中出現(xiàn)的幾個要點。首先,什么是“驅動器源極引腳”?

驅動器源極引腳是應用了開爾文連接原理的源極引腳。開爾文連接是通過電阻測量中的4個引腳或四線檢測方式,在電流路徑基礎上加上兩條測量電壓的線路,以極力消除微小電阻測量或大電流條件下測量時不可忽略的線纜電阻和接觸電阻的影響的方法,是一種廣為人知的方法。這種4引腳封裝僅限源極,通過使連接柵極驅動電路返回線的源極電壓引腳與流過大電流的電源源極引腳獨立,來消除ID對柵極驅動電路的影響。

-也就是說基本的思路就是開爾文連接對吧。

是??!稍后會給您看實際的封裝,首先我來介紹一下驅動器源極引腳對降低開關損耗的貢獻。

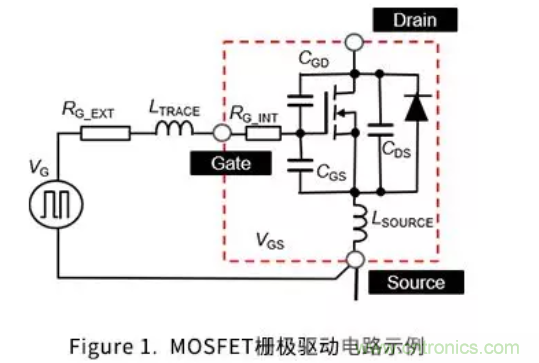

MOSFET通常為電壓驅動,通過控制柵極引腳的電壓來導通/關斷MOSFET。Figure 1為以往的3引腳封裝(TO-247N)MOSFET的常規(guī)柵極驅動電路示例。紅色虛線表示MOSFET封裝內部和外部的邊界。

通常,在驅動電源VG和MOSFET的柵極引腳之間,會插入用來控制開關速度的外置柵極電阻RG_EXT,而且還包含印刷電路板的布線電感LTRACE。另外,在源極引腳和內部的MOSFET芯片之間,包含封裝電感LSOURCE。

在寄生分量中,柵極引腳的封裝電感包含在LTRACE中,而漏極引腳的封裝電感LDRAIN不包含在柵極驅動電路中,因此在這里省略。

-這就涉及到MOSFET驅動中基本的柵極電阻和寄生分量了吧。

是的。但是,如果是普通IGBT的開關速度的話,可能不會造成很大影響,但在SiC MOSFET的特點之一“高速開關”條件下,開關的漏極-源極間電流ID的轉換和LSOURCE引起的電動勢VLSOURCE就成了問題。

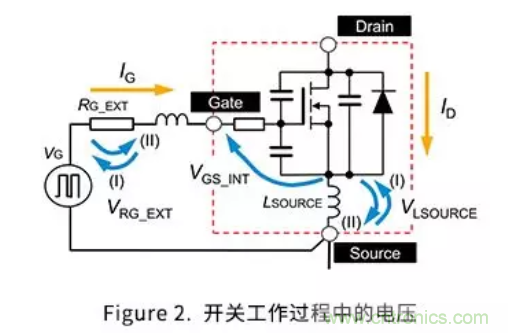

我們用Figure 2來更具體一點進行說明。Figure 2表示在開關工作中的電路內部電壓情況。

當MOSFET被施加VG并導通后,ID急劇增加,LSOURCE產(chǎn)生圖中的電動勢VLSOURCE(Ⅰ)。

由于電流IG流入柵極引腳,因此RG_EXT產(chǎn)生電壓降VRG_EXT(Ⅰ)。

雖然柵極線路的LTRACE也以相同的機制產(chǎn)生電動勢,但非常小,影響很小,因此在此省略。

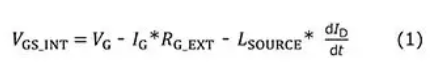

這些電壓包含在導通時的驅動電路網(wǎng)中,因此,實際上施加給內部芯片并使MOSFET導通的電壓VGS_INT減少了。VGS_INT的減少可以通過公式(1)來表示。

-也就是說,實際上施加給內部芯片的VGS_INT,是從柵極施加電壓VG減去外置柵極電阻的電壓降和源極引腳寄生電感的電動勢之后的電壓對吧。

是的。當VGS_INT減少后,MOSFET導通的速度(即開關)就會變慢。

關斷時也同樣適用公式(1)。但是,由于IG和dID/dt變?yōu)樨摂?shù),因此RG_EXT和LSOURCE產(chǎn)生標記為(Ⅱ)的電壓上升,VGS_INT反而增加。增加后使關斷速度下降。

-關于您提到RG_EXT和LSOURCE會導致開關速度下降,RG_EXT是外置的柵極電阻,因此只要減小電阻值就可以減少影響了吧?

如您所述,通過減小RG_EXT是可以提高開關速度的。RG_EXT本來是用來調整開關速度的,在這里應該理解如果RG_EXT大于所需的值,就會不必要地降低開關速度,而且開關損耗會增加。

另外,LSOURCE是封裝內部的寄生分量,因此無法從外部進行調整。這是非常重要的一點。一般來講,電源開關元器件的LSOURCE為幾nH到十幾nH,加上當dID/dt達到幾A/ns時可能會產(chǎn)生10V以上的電動勢VLSOURCE,這些將對開關工作產(chǎn)生很大的影響。

-前面看到數(shù)學公式時我還有些疑問,現(xiàn)在基本理解了。

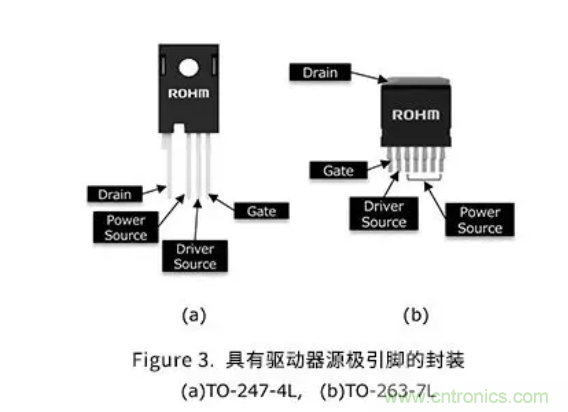

您可能已經(jīng)猜到,要想消除這種VLSOURCE的影響,就需要改變封裝的結構。我們因此而采用了電源源極和驅動器用源極分開的4引腳封裝。

抱歉引言有些長。下面是4引腳封裝的示例。目前ROHM已經(jīng)推出的產(chǎn)品有(a)TO-247-4L和(b)TO-263-7L。

推薦閱讀: