【導(dǎo)讀】英飛凌最近推出了系列650V混合SiC單管(TO247-3pin和TO-247-4pin)��。用最新的650V/SiC/G6/SBD續(xù)流二極管�����,取代了傳統(tǒng)Si的Rapid1快速續(xù)流二極管���,配合650V/TS5的IGBT芯片(S5/H5)�,進(jìn)一步優(yōu)化了系統(tǒng)效率�、性能與成本之間的微妙平衡。

IGBT混搭SiC SBD續(xù)流二極管��,在硬換流的場(chǎng)合����,至少有兩個(gè)主要優(yōu)勢(shì):

● 沒有Si二極管的反向恢復(fù)損耗Erec

● 降低30%以上IGBT的開通損耗Eon

因此��,在中小功率光伏與UPS等領(lǐng)域�,IGBT混搭SiC SBD續(xù)流二極管具有較高性價(jià)比。

此次�����,我們將利用英飛凌強(qiáng)大且豐富的器件SPICE模型���,同樣在Simetirx的仿真環(huán)境里�����,測(cè)試不同類型的續(xù)流二極管���,對(duì)IGBT開通特性及Eon的影響���。

特別提醒

仿真無法替代實(shí)驗(yàn),僅供參考����。

選取仿真研究對(duì)象

IGBT:650V/50A/S5、TO247-4pin(免去發(fā)射極電感對(duì)開通的影響)

FWD:650V/30A/50A Rapid1二極管和650V/20A/40A SiC/G6/SBD二極管

Driver IC:1EDI20I12AF驅(qū)動(dòng)芯片���,隔離單通道���,適合快速IGBT和SiC驅(qū)動(dòng)

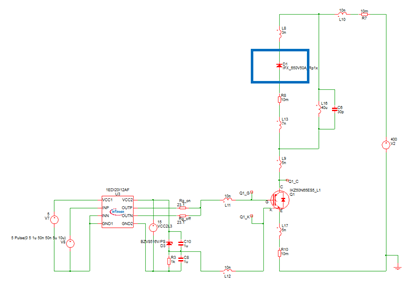

搭建仿真電路

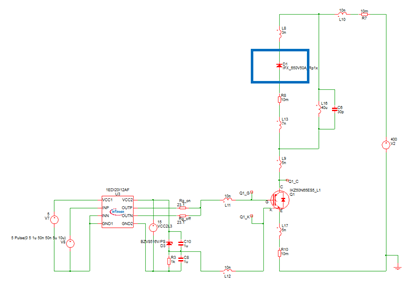

如下圖1所示,搭建了雙脈沖仿真電路��,溫度設(shè)為常溫�����。

驅(qū)動(dòng)回路

驅(qū)動(dòng)芯片(1EDI20I12AF)�����,對(duì)下管Q1(IKZ50N65ES5)門級(jí)的開關(guān)控制,與上管D1續(xù)流二極管進(jìn)行換流�。參照Datasheet的條件,驅(qū)動(dòng)IC原邊5V供電及5V的控制信號(hào)�,驅(qū)動(dòng)IC輸出的驅(qū)動(dòng)電壓15V/0V給到Q1的門級(jí),驅(qū)動(dòng)電阻Rgon和Rgoff都設(shè)置為23.1Ω����,再假設(shè)20nH左右的門級(jí)PCB走線電感。

主回路部分

設(shè)置母線電壓400V���,在器件外的上管�����、下管和母線附近各設(shè)置10nH,總共30nH(參照規(guī)格書中的雙脈沖測(cè)試條件�,Lσ=30nH)。根據(jù)仿真中的驅(qū)動(dòng)脈沖寬度與開關(guān)電流要求�,設(shè)置雙脈沖的電感參數(shù)。

圖1:雙脈沖仿真電路圖

仿真結(jié)果分析

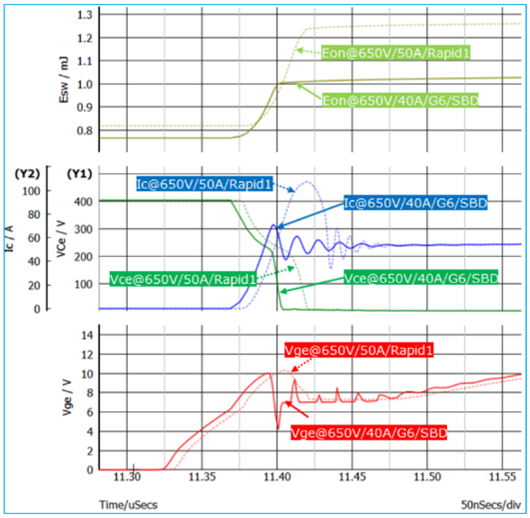

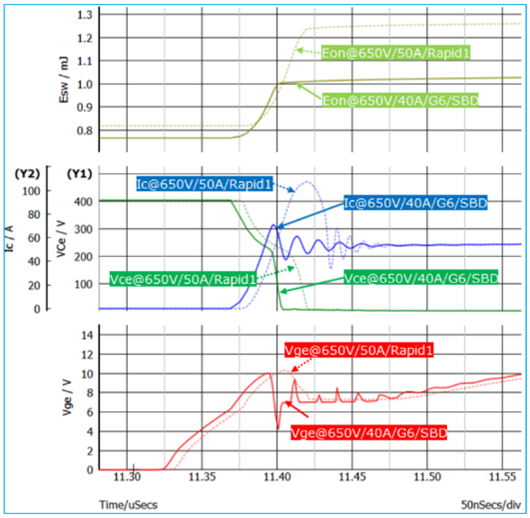

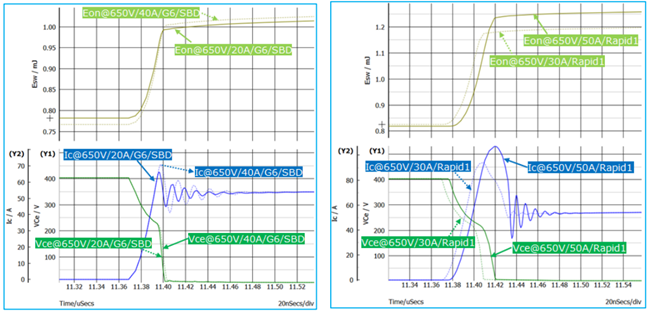

根據(jù)上述電路��,通過選取不同的續(xù)流二極管D1的型號(hào)進(jìn)行仿真�����,對(duì)比觀察Q1的IGBT在開通過程的變化。如圖2和圖3所示�����,在IGBT的開通過程中���,當(dāng)續(xù)流管D1的型號(hào)從650V/50A/Rapid1切換到650V/40A/SiC/G6/SBD后�,開通電流Ic的電流尖峰(由D1的反向恢復(fù)電荷Qrr形成)�����,從虛線(50A/Rapid1)的巨大包絡(luò)�����,顯著變?yōu)閷?shí)線(40A/SBD)的小電流過沖���;同時(shí)電壓Vce在第二段的下降速度也明顯加快��,使得電流Ic與電壓Vce的交疊區(qū)域變小����。因此,體現(xiàn)在開通損耗Eon上����,前者虛線(50A/Rapid1)為Eon=430uJ,降為實(shí)線(40A/SBD)的Eon=250uJ�����,占比為58%��,即Eon降幅約40%����。

圖2:雙脈沖仿真開關(guān)特性波形(650V/50A/Rapid1)

圖3:雙脈沖仿真開通波形對(duì)比(Rapid1/50A VS SiC/G6/SBD/40A)

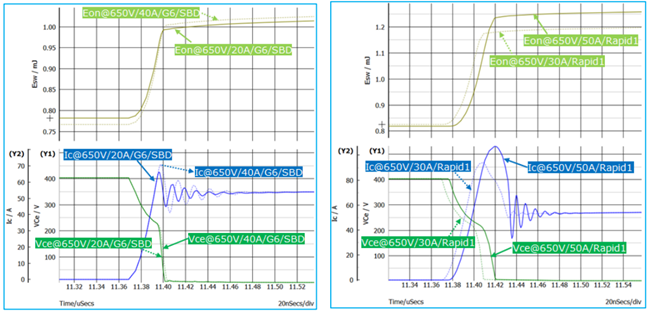

圖4:雙脈沖仿真開通波形對(duì)比(不同電流規(guī)格二極管的對(duì)比)

為了進(jìn)一步驗(yàn)證二極管D1的影響,分別用兩種不同電流進(jìn)行橫向?qū)Ρ?�。由上述圖4的仿真結(jié)果可見:同為650V/SiC/G6/SBD二極管的Qrr本身很小�����,不同電流規(guī)格(40A和20A)�,其Ic電流尖峰和開通損耗Eon都很接近�。相對(duì)而言,50A和30A的650V/Rapid1的二極管�����,才能體現(xiàn)出一定的差異。

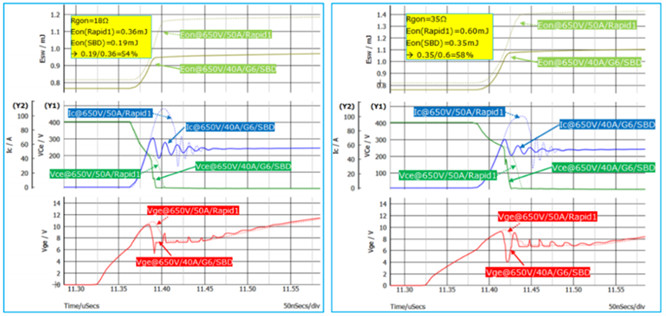

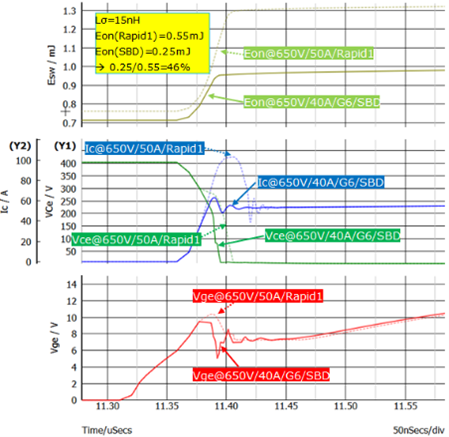

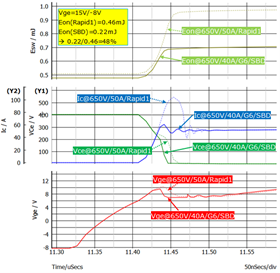

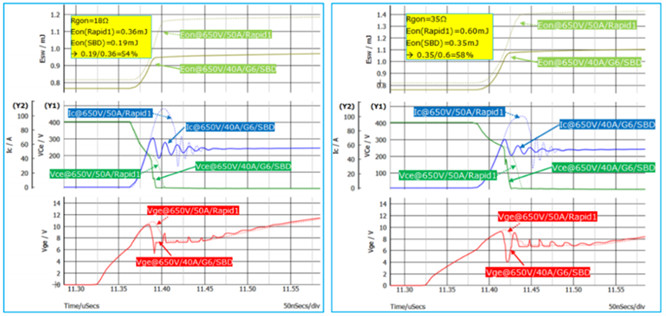

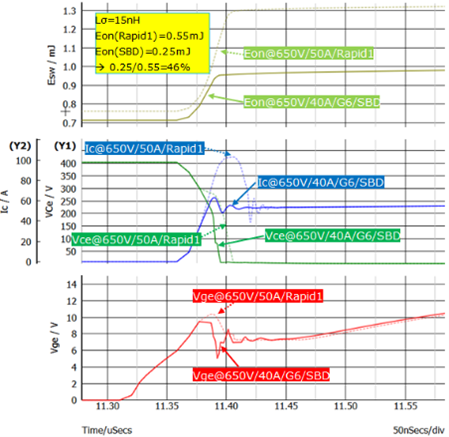

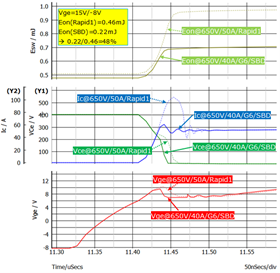

以上仿真是在門級(jí)電阻Rgon=23.1Ω���、驅(qū)動(dòng)電壓Vge=15V/0V和外部電感Lσ=30nH的條件下進(jìn)行的��,如果采用不同門級(jí)電阻Rgon=18Ω或35Ω��、Vge=15V/-8V和不同外部電感(如Lσ=15nH)時(shí)�,從Rapid1/50A到SiC/G6/SBD/40A�����,IGBT開通損耗Eon的變化趨勢(shì)又將如何呢��?

圖5:門級(jí)電阻Rgon為18Ω和35Ω時(shí)�����,SiC/G6/SBD/40A對(duì)Eon的影響

圖6:外部電感Lσ=15nH時(shí)����,SiC/G6/SBD/40A對(duì)Eon的影響

圖7:在門級(jí)電壓Vge=15V/-8V時(shí),SiC/G6/SBD/40A對(duì)Eon的影響

由上述幾組仿真結(jié)果來看���,在一定門級(jí)電阻Rgon范圍��,一定外部電感條件Lσ���,以及不同門級(jí)電壓Vge時(shí)����,均可以看到650V/40A/SiC/SBD二極管���,給IGBT開通帶來約50%左右的Eon損耗降低���。

文章最后,我們?cè)儆懻撘粋€(gè)問題:選擇Vge=15V/0V與Vge=15V/-8V�����,對(duì)650V/50A/S5的TO247-4pin的單管的開關(guān)損耗Eon/Eoff有影響嗎����?

圖8:不同Vge電壓對(duì)650V/S5/50A+Rapid1/50A開關(guān)特性的影響

圖9:不同Vge電壓對(duì)650V/S5/50A+SiC/G6/SBD/40A開關(guān)特性的影響

在圖8和圖9中,虛線表示Vge=15V/0V���,而實(shí)線表示Vge=15V/-8V���;粗略來看,對(duì)Eon的影響可以忽略���,而對(duì)Vge的負(fù)壓��,可以減少Eoff差不多有50%(以Vce尖峰作為代價(jià))���。仿真雖然無法定量,至少可以定性地提醒大家��,在設(shè)計(jì)與實(shí)測(cè)的時(shí)候�,不要隨意忽視Vge對(duì)開關(guān)特性的影響,尤其是快速型的IGBT�。

期望上述的仿真分析,對(duì)大家深入理解650V混合SiC的開關(guān)特性有所幫助���。

來源:英飛凌科技大中華區(qū)

免責(zé)聲明:本文為轉(zhuǎn)載文章��,轉(zhuǎn)載此文目的在于傳遞更多信息����,版權(quán)歸原作者所有。本文所用視頻�����、圖片��、文字如涉及作品版權(quán)問題�����,請(qǐng)聯(lián)系小編進(jìn)行處理����。

推薦閱讀: