【導(dǎo)讀】變壓器繞組繞在磁芯骨架上,特別是繞組的層數(shù)較多時,不可避免的會產(chǎn)生分布電容,由于變壓器工作在高頻狀態(tài)下,這些分布電容對變壓器的工作狀態(tài)將產(chǎn)生非常大的影響,如引起波形產(chǎn)生振蕩,EMC變差,變壓器發(fā)熱等。所以我們需要優(yōu)化變壓器的匝間電容。

變壓器的分布電容主要為4個部分:繞組匝間電容,層間電容,繞組電容和雜散電容。

繞組匝間電容是將變壓器兩個相鄰的繞組比作兩塊極板,當(dāng)給兩塊極板加上適當(dāng)?shù)碾妷簳r,極板之間就會產(chǎn)生電場,并儲存電荷。

繞組的層間電容指的是每個單獨(dú)繞組各層之間的電容。在繞制變壓器時,一般會出現(xiàn)單個繞組需要繞2層或2層以上,此時的每2層之間都會形成一個電場,即會產(chǎn)生一個等效電容效應(yīng),我們把這個電容稱為層間電容。

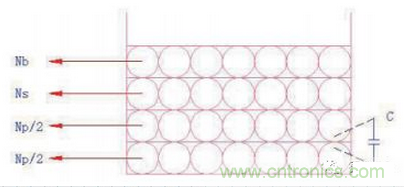

如下圖:

電容C就是層間電容

層間電容是變壓器的分布電容中對電路影響最重要的因素,因?yàn)檫@個電容會跟漏感在MOS開通與關(guān)閉的時候,產(chǎn)生振蕩,從而加大MOS與次級Diode的電壓應(yīng)力,使EMC變差。

我們可以用以下四種方法來將它的影響降到可以接受的范圍。

方法一:增大繞組的距離來減小層間電容,最有代表性的就是采用三層絕緣線。但這個方法有缺點(diǎn),因?yàn)榫€的外徑粗了之后,帶來的后果就是繞線層數(shù)的增加,增加了層間電容。

方法二:可通過選擇繞線窗口比較寬的磁芯骨架,因?yàn)槔@線窗口寬,那么單層繞線可以繞更多的匝數(shù),也意味著可以有效的降低繞線層數(shù),層間電容就有效降低了。這是最直接有效的。缺點(diǎn)就是選擇磁芯骨架要受到電源結(jié)構(gòu)尺寸的限制。

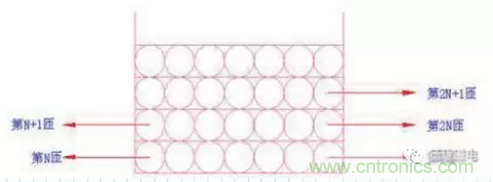

方法三:可以采用交叉堆疊繞法來降低層間電容,如下圖

此繞法有顯著缺點(diǎn),會增加初次級之間的耦合面積,也就是會加大初次級繞組之間的電容,使EMC變差。

方法四:改變繞制工藝

先來看看普通繞法

如上圖,這是我們常用的U型繞法,可以看到,在第1匝與第2N匝之間的壓差將非常大,由公式Q=C*U可知,壓差越大,在這個電容上儲存的電荷就越多,這個地方的干擾電壓斜率將非常大,在這個地方形成的干擾就越大。

我們可以采用Z型繞法降低這個影響,如下圖

此種繞法可以顯著降低電壓斜率,對EMC是非常有利的。缺點(diǎn)就是繞制工藝相對復(fù)雜。

繞組電容就是指繞組之間產(chǎn)生的電容,比如說初級繞組Np與次級繞組Ns之間的電容。由于此電容存在于初次級繞組之間,對電路的EMI是非常不利的,因?yàn)槌跫壆a(chǎn)生的共模電流信號可以通過這個電容耦合到次級中去,這就造成了非常大的共模干擾,而共模干擾可能會引起電路噪音或者輸出不穩(wěn)定。

辦法是在初次級繞組之間加一個屏蔽層,并且用這個屏蔽層接到電路中的某點(diǎn),來降低電容的影響。這種屏蔽層被稱為法拉第屏蔽層,由銅箔或者繞組構(gòu)成。在用銅箔時,我們一般會繞0.9Ts或者1.1Ts,不會繞1Ts,因?yàn)檫@樣容易短路,短路就會導(dǎo)致磁力線短路,電感就接近為零,再反射到初級,初級的電感也為零,這時候如果產(chǎn)品通電的話就會短路炸機(jī)了。

變壓器的匝間電容是我們不希望產(chǎn)生的,電容越大,對線路的干擾就越大,嚴(yán)重時會改變電路的參數(shù),甚至造成電路無法工作。所以,在設(shè)計(jì)變壓器時,應(yīng)盡量進(jìn)行合理的材料選擇,優(yōu)化繞制工藝,以達(dá)到減少匝間電容的目的。