【導(dǎo)讀】本次設(shè)計(jì)是基于FPGA 的電機(jī)測(cè)速系統(tǒng)設(shè)計(jì),利用的是Altera 公司開發(fā)的Quartus II 軟件作為設(shè)計(jì)平臺(tái)����,可以在FPGA 開發(fā)板上實(shí)現(xiàn)測(cè)量由傳感器轉(zhuǎn)換得到的脈沖信號(hào)���,并且通過計(jì)算得到電機(jī)轉(zhuǎn)速值�����。

現(xiàn)場(chǎng)可編程門陣列即FPGA����,是從EPLD����、PAL、GAL等這些可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展起來的���。作為專業(yè)集成電路領(lǐng)域中的半定制電路而出現(xiàn)的FPGA�,不但解決了定制電路的不足��,而且克服了原有可編程器件因門電路數(shù)有限的而產(chǎn)生的缺點(diǎn)�。FPGA 的使用十分的靈活,同一片F(xiàn)PGA 只要使用不同的程序就能夠達(dá)到不同的電路功能。現(xiàn)在FPGA 在通信���、儀器���、網(wǎng)絡(luò)、數(shù)據(jù)處理���、工業(yè)控制���、軍事和航空航天等眾多領(lǐng)域有著廣泛的應(yīng)用。隨著成本和功耗的進(jìn)一步降低��,將在更多的領(lǐng)域運(yùn)用FPGA��?����;贔PGA 的電機(jī)測(cè)速系統(tǒng)設(shè)計(jì)�,以Quartus II 為設(shè)計(jì)平臺(tái),采用硬件描述語(yǔ)言VHDL和模塊化設(shè)計(jì)的方式�����,并通過數(shù)碼管驅(qū)動(dòng)電路動(dòng)態(tài)顯示測(cè)量的結(jié)果���。本設(shè)計(jì)具有外圍電路少��,集成度高�����,可靠性強(qiáng)等特點(diǎn)����,可以用來測(cè)量電機(jī)的轉(zhuǎn)速值�����。

外圍電路設(shè)計(jì)

傳感器將電機(jī)轉(zhuǎn)速的模擬信號(hào)轉(zhuǎn)換成數(shù)字脈沖信號(hào)送入FPGA 模塊�。同時(shí)由基準(zhǔn)時(shí)鐘電路產(chǎn)生準(zhǔn)確的時(shí)鐘信號(hào)和復(fù)位電路產(chǎn)生的復(fù)位信號(hào)送入FPGA 模塊。再由FPGA 模塊產(chǎn)生分頻電路�、十進(jìn)制計(jì)數(shù)器電路、數(shù)據(jù)處理電路和顯示譯碼電路�����。由分頻電路將送入的基準(zhǔn)時(shí)鐘信號(hào)進(jìn)行分頻���,得到一個(gè)閘門信號(hào)�,作為十進(jìn)制計(jì)數(shù)器的使能信號(hào)。數(shù)據(jù)處理電路的作用是將十進(jìn)制計(jì)數(shù)器得到的數(shù)據(jù)進(jìn)行相應(yīng)的處理后�����,再送入顯示譯碼電路進(jìn)行轉(zhuǎn)換譯碼����。電機(jī)測(cè)速系統(tǒng)的總體框圖如圖1所示。外圍電路分為:基準(zhǔn)時(shí)基電路����,復(fù)位電路,傳感器測(cè)量電路和顯示電路�����。

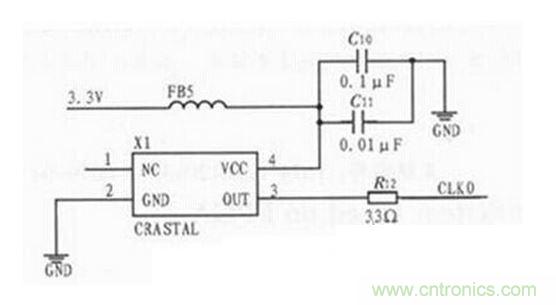

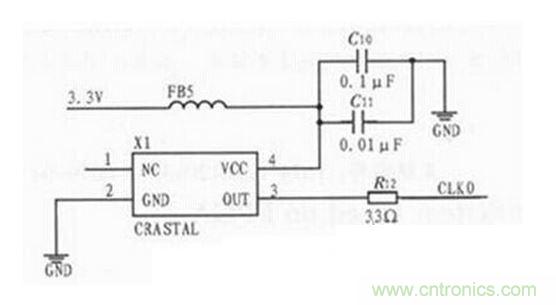

基準(zhǔn)時(shí)基電路設(shè)計(jì)

基準(zhǔn)時(shí)基電路采用50 MHz 的有源晶振����,3.3 V 電源通過FB5接入有源晶振的VCC 端口,同時(shí)通過C10和C11濾去高頻干擾信號(hào)����。從OUT 端口輸出50 MHz 的時(shí)鐘信號(hào)����。晶振電路如圖2所示��。

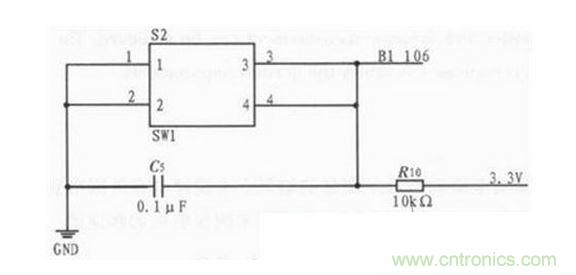

復(fù)位按鍵的設(shè)計(jì)

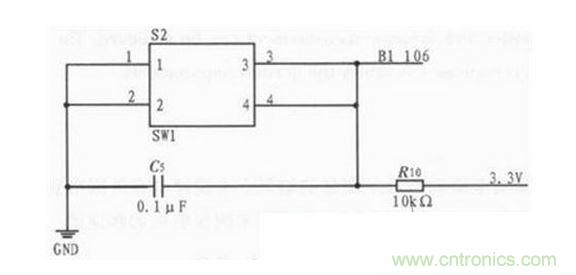

按鍵作為嵌入式智能控制系統(tǒng)中人機(jī)交互的常用接口�,我們通常會(huì)通過按鍵向系統(tǒng)輸入各種信息���,調(diào)整各種參數(shù)或者發(fā)出控制指令����,按鍵的處理是一個(gè)很重要的功能模塊��,它關(guān)系到整個(gè)系統(tǒng)的交互性能��,同時(shí)也影響系統(tǒng)的穩(wěn)定性�����。在本次設(shè)計(jì)中����,通過按鍵實(shí)現(xiàn)了FPGA模塊的手動(dòng)復(fù)位。復(fù)位按鍵如圖3所示��。

圖3 復(fù)位按鍵電路圖

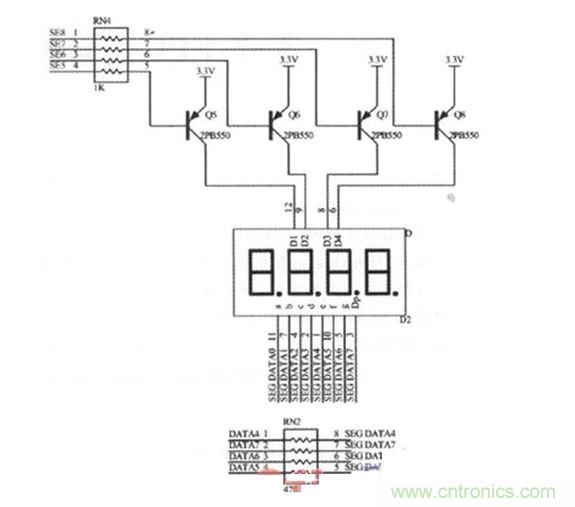

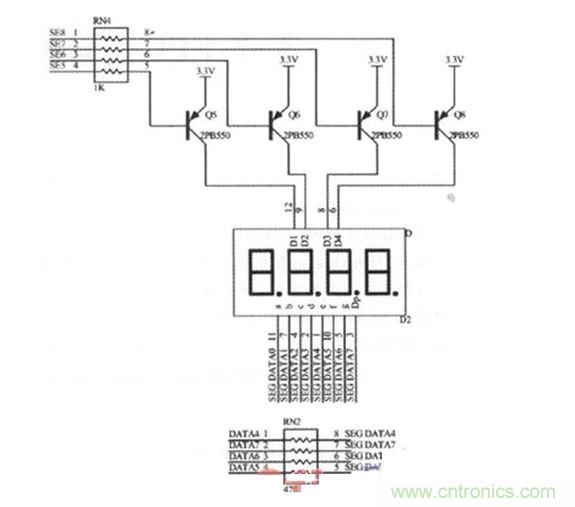

顯示電路的設(shè)計(jì)

在本次設(shè)計(jì)中我們用到的顯示電路如圖4 所示。

由數(shù)碼管顯示電路可以知道����,這是共陽(yáng)極數(shù)碼管。當(dāng)在位選端SE1~SE4輸入低電平時(shí)��,三極管導(dǎo)通�,從而D1~D4接入高電平。由a 到DP 端輸入數(shù)碼管顯示碼����,就可以得到我們所需要的數(shù)字,由位選端讓數(shù)碼管選擇導(dǎo)通����。

本次設(shè)計(jì)是基于FPGA 的電機(jī)測(cè)速系統(tǒng)設(shè)計(jì),利用的是Altera 公司開發(fā)的Quartus II 軟件作為設(shè)計(jì)平臺(tái)����,可以在FPGA 開發(fā)板上實(shí)現(xiàn)測(cè)量由傳感器轉(zhuǎn)換得到的脈沖信號(hào),并且通過計(jì)算得到電機(jī)轉(zhuǎn)速值����。在本次設(shè)計(jì)中,還可以進(jìn)行一些擴(kuò)展�����,可以添加報(bào)警電路,設(shè)定一個(gè)報(bào)警值�����,當(dāng)測(cè)量的轉(zhuǎn)速值大于這個(gè)報(bào)警值時(shí)����,就可以讓蜂鳴器報(bào)警或數(shù)碼管點(diǎn)亮���。