【導(dǎo)讀】以下為大家總結(jié)了58條有關(guān)的模擬�����、數(shù)字電路基礎(chǔ)知識(shí)。HC為COMS電平�����,HCT為TTL電平���;LS輸入開路為高電平���,HC輸入不允許開路, HC一般都要求有上下拉電阻來確定輸入端無(wú)效時(shí)的電平��。LS 卻沒有這個(gè)要求���。

1、 HC為COMS電平�����,HCT為TTL電平

2��、 LS輸入開路為高電平�,HC輸入不允許開路, HC一般都要求有上下拉電阻來確定輸入端無(wú)效時(shí)的電平���。LS 卻沒有這個(gè)要求

3�����、 LS輸出下拉強(qiáng)上拉弱�����,HC上拉下拉相同

4���、 工作電壓:LS只能用5V��,而HC一般為2V到6V

5����、 CMOS可以驅(qū)動(dòng)TTL���,但反過來是不行的���。TTL電路驅(qū)動(dòng)COMS電路時(shí)需要加上拉電阻,將2.4V~3.6V之間的電壓上拉起來����,讓CMOS檢測(cè)到高電平輸入

6、 驅(qū)動(dòng)能力不同,LS一般高電平的驅(qū)動(dòng)能力為5mA�,低電平為20mA;而CMOS的高低電平均為5mA

7���、 RS232電平為+12V為邏輯負(fù)��,-12為邏輯正

8��、 74系列為商用��,54為軍用

9�����、 TTL高電平>2.4V,TTL低電平<0.4V, 噪聲容限0.4V

10��、 OC門,即集電極開路門電路(為什么會(huì)有OC門?因?yàn)橐獙?shí)現(xiàn)“線與”邏輯)����,OD門,即漏極開路門電路����,必須外界上拉電阻和電源才能將開關(guān)電平作為高低電平用。否則它一般只作為開關(guān)大電壓和大電流負(fù)載,所以又叫做驅(qū)動(dòng)門電路�����。并且只能吸收電流���,必須外界上拉電阻和電源才才能對(duì)外輸出電流

11�、 COMS的輸入電流超過1mA�����,就有可能燒壞COMS

12���、 當(dāng)接長(zhǎng)信號(hào)傳輸線時(shí)�,在COMS電路端接匹配電阻

13�����、 在門電路輸入端串聯(lián)10K電阻后再輸入低電平���,輸入端出呈現(xiàn)的是高電平而不是低電平

14��、 如果電路中出現(xiàn)3.3V的COMS電路去驅(qū)動(dòng)5V CMOS電路的情況��,如3.3V單片機(jī)去驅(qū)動(dòng)74HC,這種情況有以下幾種方法解決��,最簡(jiǎn)單的就是直接將74HC換成74HCT的芯片��,因?yàn)?.3VCMOS 可以直接驅(qū)動(dòng)5V的TTL電路;或者加電壓轉(zhuǎn)換芯片;還有就是把單片機(jī)的I/O口設(shè)為開漏�����,然后加上拉電阻到5V�,這種情況下得根據(jù)實(shí)際情況調(diào)整電阻的大小,以保證信號(hào)的上升沿時(shí)間����。

15、 邏輯門輸出為高電平時(shí)的負(fù)載電流(為拉電流)����,邏輯門輸出為低電平時(shí)的負(fù)載電流(為灌電流)

16、 由于漏級(jí)開路���,所以后級(jí)電路必須接一上拉電阻,上拉電阻的電源電壓就可以決定輸出電平���。這樣漏極開路形式就可以連接不同電平的器件��,用于電平轉(zhuǎn)換��。需要注意的一點(diǎn):在上升沿的時(shí)候通過外部上拉無(wú)源電阻對(duì)負(fù)載進(jìn)行充電�����,所以上升沿的時(shí)間可能不夠迅速�,盡量使用下降沿

17、 幾種電平轉(zhuǎn)換方法:

就是一個(gè)雙極型三極管或 MOSFET�����,C/D極接一個(gè)上拉電阻到正電源���,輸入電平很靈活�,輸出電平大致就是正電源電平�。

(2) OC/OD 器件+上拉電阻法

跟 (1) 類似。適用于器件輸出剛好為 OC/OD 的場(chǎng)合���。

(3) 74xHCT系列芯片升壓 (3.3V→5V)

凡是輸入與 5V TTL 電平兼容的 5V CMOS 器件都可以用作 3.3V→5V 電平轉(zhuǎn)換���。這是由于 3.3V CMOS 的電平剛好和5VTTL電平兼容(巧合),而 CMOS 的輸出電平總是接近電源電平的��。廉價(jià)的選擇如 74xHCT(HCT/AHCT/VHCT/AHCT1G/VHCT1G/...) 系列 (那個(gè)字母 T 就表示TTL 兼容)。

(4) 超限輸入降壓法 (5V→3.3V,3.3V→1.8V, ...)

凡是允許輸入電平超過電源的邏輯器件����,都可以用作降低電平。這里的"超限"是指超過電源��,許多較古老的器件都不允許輸入電壓超過電源�����,但越來越多的新器件取消了這個(gè)限制 (改變了輸入級(jí)保護(hù)電路)�。例如,74AHC/VHC 系列芯片����,其 datasheets 明確注明"輸入電壓范圍為0~5.5V",如果采用3.3V 供電����,就可以實(shí)現(xiàn) 5V→3.3V 電平轉(zhuǎn)換。

(5) 專用電平轉(zhuǎn)換芯片

最著名的就是 164245�����,不僅可以用作升壓/降壓���,而且允許兩邊電源不同步��。這是最通用的電平轉(zhuǎn)換方案����,但是也是很昂貴的 (俺前不久買還是¥45/片�,雖是零售,也貴的嚇人)�����,因此若非必要�,最好用前兩個(gè)方案。

(6) 電阻分壓法

最簡(jiǎn)單的降低電平的方法���。5V電平����,經(jīng)1.6k+3.3k電阻分壓����,就是3.3V。

(7) 限流電阻法

18��、 無(wú)極性電容和有極性電容:前者的封裝基本為0805,0603���。后者用的最多為鋁電解電容����,好一點(diǎn)的鉭電容

19�����、 PQFP(Plastic Quad Flat Package, 塑料四邊引出扁平封裝), BGA(Ball Grid Array Package, 球柵陣列封裝), PGA(Pin Grid Array Package, 針柵陣列封裝), PLCC(Plastic Leaded Chip Carrier, 塑料有引線芯片載體), SOP(Small Outline Package, 小尺寸封裝), TOSP(Thin Small Outline Package, 薄小外形封裝), SOIC(Small Outline Integrated Circuit Package, 小外形集成電路封裝)

20����、 集成電路常見的封裝形式

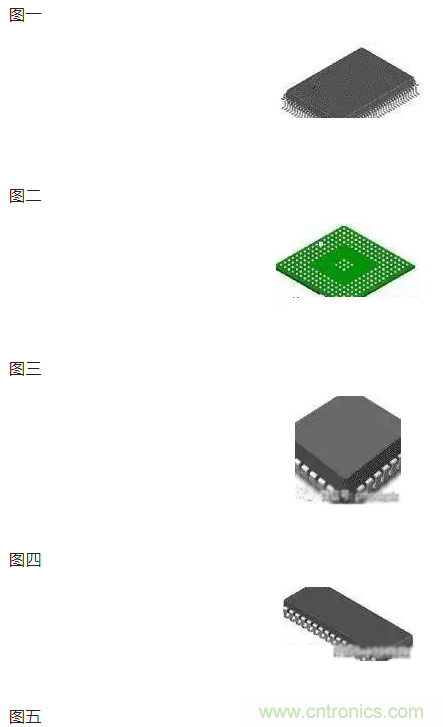

QFP(quad flat package) 四面有鷗翼型腳(封裝) 見圖一

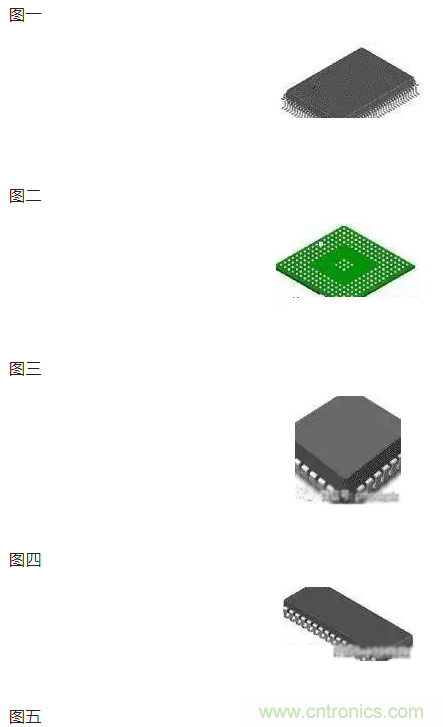

BGA(ball grid array) 球柵陣列(封裝) 見圖二

PLCC(plastic leaded chip carrier) 四邊有內(nèi)勾型腳(封裝) 見圖三

SOJ(small outline junction) 兩邊有內(nèi)勾型腳(封裝) 見圖四

SOIC(small outline integrated circuit) 兩面有鷗翼型腳(封裝) 見圖五

21、 屏蔽線對(duì)靜電有很強(qiáng)的抑制作用���,雙絞線對(duì)電磁感應(yīng)也有一定的抑制效果

22���、 模擬信號(hào)采樣抗干擾技術(shù):可以采用具有差動(dòng)輸入的測(cè)量放大器,采用屏蔽雙膠線傳輸測(cè)量信號(hào)��,或?qū)㈦妷盒盘?hào)改變?yōu)殡娏餍盘?hào)���,以及采用阻容濾波等技術(shù)

23��、 閑置不用的IC管腳不要懸空以避免干擾引入��。不用的運(yùn)算放大器正輸入端接地����,負(fù)輸入端接輸出��。單片機(jī)不用的I/O口定義成輸出��。單片機(jī)上有一個(gè)以上電源���、接地端���,每個(gè)都要接上,不要懸空

24��、 電阻阻值色環(huán)表示法:普通的色環(huán)電阻器用4環(huán)表示,精密電阻器用5環(huán)表示

25�、 電阻的作用為分流、限流�、分壓、偏置、濾波(與電容器組合使用)和阻抗匹配等

26、 電容的作用:隔直流,旁路,耦合,濾波,補(bǔ)償,充放電,儲(chǔ)能等

27����、 一般電容的數(shù)字表示法單位為pF��,電解電容一般為uF

28、 電容器的主要性能指標(biāo):電容器的容量(即儲(chǔ)存電荷的容量), 耐壓值(指在額定溫度范圍內(nèi)電容能長(zhǎng)時(shí)間可靠工作的最大直流電壓或最大交流電壓的有效值) 耐溫值(表示電容所能承受的最高工作溫度)

29��、 電感器的作用:濾波�,陷波,振蕩��,儲(chǔ)存磁能等

30�����、 電感器的分類:空芯電感和磁芯電感.磁芯電感又可稱為鐵芯電感和銅芯電感等

31�、 半導(dǎo)體二極管的分類

a) 按材質(zhì)分:硅二極管和鍺二極管;

b) 按用途分:整流二極管,檢波二極管��,穩(wěn)壓二極管����,發(fā)光二極管,光電二極管�,變?nèi)荻O管。

32�����、 場(chǎng)效應(yīng)管是電壓控制元件,而晶體管是電流控制元件�����。在只允許從信號(hào)源取較少電流的情況下��,應(yīng)選用場(chǎng)效應(yīng)管;而在信號(hào)電壓較低�,又允許從信號(hào)源取較多電流的條件下�����,應(yīng)選用晶體管

33�、 Socket是一種插座封裝形式,是一種矩型的插座;Slot是一種插槽封裝形式,是一種長(zhǎng)方形的插槽

34、 晶振的測(cè)量方法:用萬(wàn)用表RX10K檔測(cè)量石英晶體振蕩器的正,反向電阻值.正常時(shí)應(yīng)為無(wú)窮大.若測(cè)得石英晶體振蕩器有一定的阻值或?yàn)榱?則說明該石英晶體振蕩器已漏電或擊穿損壞

35��、 IO口輸出高電平時(shí)��,驅(qū)動(dòng)能力最低�,對(duì)外顯示為推電流;IO口輸出低電平時(shí),驅(qū)動(dòng)能力最大����,對(duì)外顯示為拉電流

36、 外圍集成數(shù)字驅(qū)動(dòng)電路如果驅(qū)動(dòng)的是感性負(fù)載,必須加限流電阻或鉗住二極管

37�、 9013提供的驅(qū)動(dòng)電流有300mA

38、 輸出數(shù)據(jù)應(yīng)該鎖存(外圍速度跟不上��,所以需要鎖存)�����,輸入數(shù)據(jù)應(yīng)該有三態(tài)緩沖(加入了高阻狀態(tài)����,不至于對(duì)內(nèi)部的數(shù)據(jù)總線產(chǎn)生影響)

39、 8位并行輸出口(必須帶有鎖存功能):74LS377,74LS273.8位并行輸入口(必須是三態(tài)門):74LS373,74LS244

40����、 串行口擴(kuò)展并行口,并行輸入口:74LS165���。并行輸出口:74LS164

41���、 鍵盤工作方式有三種:

l 編程掃描方式

l 定時(shí)掃描方式

l 中斷方式。還可以專門設(shè)計(jì)一個(gè)IO口用來進(jìn)行雙功能鍵的設(shè)計(jì)(上檔鍵和下檔鍵)

42�����、 對(duì)于TTL負(fù)載,主要應(yīng)考慮直流負(fù)載特性��,因?yàn)門TL的電流大���,分布電容小�����。對(duì)于MOS型負(fù)載��,主要應(yīng)考慮交流負(fù)載特性����,因?yàn)镸OS型負(fù)載的輸入電流小����,主要考慮分布電容

43�、 特別注意總線負(fù)載平衡的概念!

44、 上拉電阻的好處:

l 提高信號(hào)電平

l 提高總線的抗電磁干擾能力(電磁信號(hào)通過DB進(jìn)入CPU)

l 抑制靜電干擾(CMOS芯片)

l 反射波干擾(長(zhǎng)遠(yuǎn)距離傳輸)

45�、 穩(wěn)壓時(shí),采用兩級(jí)集成穩(wěn)壓芯片穩(wěn)壓效果更好

46�����、 傳輸線的阻抗匹配:

l 終端并聯(lián)阻抗匹配(高電平下降)

l 始端串聯(lián)匹配(低電平抬高)

l 終端并聯(lián)隔直流匹配(RC串聯(lián)接地)

l 終端接鉗位二極管

47、 接地分兩種:外殼接地(真正的接地)和工作接地(浮地)

48���、 在單片機(jī)中地的種類:數(shù)字地�����,模擬地����,功率地(電流大�,地線粗),信號(hào)地���,交流地��,屏蔽地

49�、 一點(diǎn)接地:低頻電路(1MHZ以下)�����。多點(diǎn)接地:高頻電路(10MHZ以上)

50��、 交流地與信號(hào)地不能公用����,數(shù)字地和模擬地最好分開���,然后在一點(diǎn)相連

51、 揩振回路:可以選用云母���、高頻陶瓷電容�,隔直流:可以選用紙介���、滌綸�����、云母���、電解、陶瓷等電容�,濾波:可以選用電解電容�����,旁路:可以選用滌綸�����、紙介�����、陶瓷�、電解等電容

52��、 二極管應(yīng)用電路

(1) 限幅電路---利用二極管單向?qū)щ娦院蛯?dǎo)通后兩端電壓基本不變的特點(diǎn)組成�����,將信號(hào)限定在某一范圍中變化�����,分為單限幅和雙限幅電路�。多用于信號(hào)處理電路中。

(2) 箝位電路---將輸出電壓箝位在一定數(shù)值上����。

(3) 開關(guān)電路---利用二極管單向?qū)щ娦砸越油ê蛿嚅_電路����,廣泛用于數(shù)字電路中����。

(4) 整流電路---利用二極管單向?qū)щ娦裕瑢⒔涣餍盘?hào)變?yōu)橹绷餍盘?hào)���,廣泛用于直流穩(wěn)壓電源中���。

(5) 低電壓穩(wěn)壓電路---利用二極管導(dǎo)通后兩端電壓基本不變的特點(diǎn),采用幾只二極管串聯(lián)����,獲得3V以下輸出電壓

53�����、 高頻旁路電容一般比較小,根據(jù)諧振頻率一般是0.1u����,0.01u等,而去耦合電容一般比較大��,是10uF或者更大

54��、 上拉電阻總結(jié):

l 當(dāng)TTL電路驅(qū)動(dòng)COMS電路時(shí)�,如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),這時(shí)就需要在TTL的輸出端接上拉電阻��,以提高輸出高電平的值�。

l OC門電路必須加上拉電阻,才能使用���。

l 為加大輸出引腳的驅(qū)動(dòng)能力�����,有的單片機(jī)管腳上也常使用上拉電阻�����。

l 在COMS芯片上�,為了防止靜電造成損壞,不用的管腳不能懸空����,一般接上拉電阻產(chǎn)生降低輸入阻抗,提供泄荷通路����。

l 芯片的管腳加上拉電阻來提高輸出電平,從而提高芯片輸入信號(hào)的噪聲容限增強(qiáng)抗干擾能力���。

l 提高總線的抗電磁干擾能力�����。管腳懸空就比較容易接受外界的電磁干擾�。

l 長(zhǎng)線傳輸中電阻不匹配容易引起反射波干擾��,加上下拉電阻是電阻匹配���,有效的抑制反射波干擾��。

55���、 從節(jié)約功耗及芯片的灌電流能力考慮應(yīng)當(dāng)足夠大��;電阻大�����,電流小�����。

從確保足夠的驅(qū)動(dòng)電流考慮應(yīng)當(dāng)足夠?����。浑娮栊?��,電流大�����。

56�����、 上拉就是將不確定的信號(hào)通過一個(gè)電阻嵌位在高電平!電阻同時(shí)起限流作用!下拉同理

57��、 旁路電容:產(chǎn)生一個(gè)交流分路��,從而消去進(jìn)入易感區(qū)的那些不需要的能量�。去耦電容:提供一個(gè)局部的直流電源給有源器件��,以減少開關(guān)噪聲在板上的傳播和將噪聲引導(dǎo)到地(他的取值大約為旁路電容的1/100到1/1000)

58����、 有源蜂鳴器:內(nèi)部有振蕩電路,通電就可以響�。無(wú)源蜂鳴器:內(nèi)部沒有振蕩電路,需要外加2K-5K的方波信號(hào)才能響�。