【導(dǎo)讀】IEEE 1588標準誕生于2002 年,主要定義網(wǎng)絡(luò)分布式時鐘的同步協(xié)議�����。測試與測量�、電信和多媒體流處理等許多不同應(yīng)用,都開始首選這種時鐘同步方法�。這種標準化時鐘同步法成本效益高,支持異構(gòu)系統(tǒng)�,并可提供納秒級同步精度。

本文介紹原版 IEEE 1588-2002 標準以及更新版本 IEEE 1588-2008 中的改進內(nèi)容�����。由于IEEE 1588 在一些目標應(yīng)用中越來越重要,因此 ADSP-BF5181 Blackfin® 嵌入式處理器中也集成專用硬件來支持IEEE 1588����。本文將概要介紹其功能,并通過一個示例來展示利用ADSP-BF518 處理器解決方案獲得的時鐘同步性能結(jié)果��。

現(xiàn)在幾點了���?

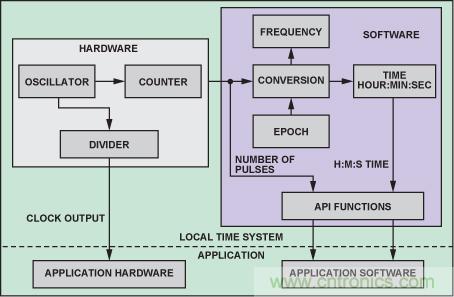

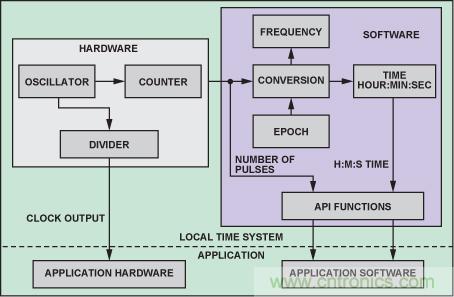

大多數(shù)系統(tǒng)都需要利用本振來維護自己的時間概念����。圖1顯示硬件和軟件如何組合����,在系統(tǒng)內(nèi)產(chǎn)生時間信息

圖1. 本地計時

系統(tǒng)內(nèi)的硬件和軟件資源均可使用此時間信息。對于硬件�,振 蕩器時鐘會產(chǎn)生一個或多個物理時鐘信號(時鐘輸出)����,并可 利用這些時鐘信號驅(qū)動或觸發(fā)系統(tǒng)的其它部分。軟件中維護的 時間通常稱為"系統(tǒng)時間"���。系統(tǒng)時間可以用時鐘脈沖數(shù)或秒 / 納秒的形式表示���。系統(tǒng)軟件利用振蕩器時鐘脈沖數(shù)及其頻率 信息得出時間�,并提供"應(yīng)用程序編程接口" (API) 函數(shù)�����,軟 件的其它部分可以使用這些函數(shù)檢索并設(shè)置時間�。如果需要絕 對時間,則所提供的時間將與預(yù)定義時間點�����,即基準時間點相 關(guān)聯(lián).

時鐘同步

許多應(yīng)用要求兩臺獨立的設(shè)備以同步方式工作�。如果每臺設(shè)備 僅依靠自己的振蕩器,則各振蕩器的特性與工作條件差異將會 限制時鐘同步工作的能力�����。一些簡單可行的解決方案可以克服 這些限制���,包括:

● 所有設(shè)備共用一個物理振蕩器.這種方法僅對距離很近的分

● 所有設(shè)備均使用特性幾乎完全相同的振蕩器.由 于很難獲得 幾乎完全一樣的振蕩器���,并確保性能不隨時間飄移�,因此這 種方法不可行�����。更重要的是�,各振蕩器的工作條件并不相

● 如果所有設(shè)備均通過一個通信網(wǎng)絡(luò)(例如以太網(wǎng))互連,則這些設(shè)備可以通過網(wǎng)絡(luò)交換時間消息�����,根據(jù)單個"主"時鐘 動態(tài)調(diào)整各自的時鐘��。利用傳統(tǒng)的時間同步協(xié)議—— "網(wǎng)絡(luò) 時間協(xié)議"(NTP)��,統(tǒng)中的每臺設(shè)備根據(jù)它從 NTP時間服 務(wù)器獲取的時間信息調(diào)整其時鐘���。然而�����,該協(xié)議只能實現(xiàn)毫 秒級同步精度�。

IEEE 1588 定義了一個新協(xié)議���,能夠?qū)崿F(xiàn)納秒級同步精度。下 面討論該標準如何實現(xiàn)這種水平的時鐘同步。

IEEE 1588 有何作用

IEEE 1588 標準定義了一種時間同步協(xié)議���,適用于地理位置分 散但通過某種通信技術(shù)(例如以太網(wǎng))互連的設(shè)備�����。設(shè)備之間 通過交換時序消息��,從而保持相同的絕對系統(tǒng)時間(用秒和納 秒表示)����。

要實現(xiàn)此目標���,一個直觀的方法是將一臺具有"最佳"(最精 確)時鐘的設(shè)備指定為"主時鐘"設(shè) 備����,讓它向其它設(shè)備廣播 其時間����。其它設(shè)備將會調(diào)整各自的時間,與主時鐘所發(fā)送的時 間保持一致����。不過�����,這種解決方案也有幾點不足:

1. 主時鐘設(shè)備無法以極短的間隔廣播時間��,因此"從"時鐘設(shè)備必須使用自己獨立的"低劣"振蕩器���,在主時鐘設(shè)備

2. 廣播路徑難免存在延遲,延遲幅度取決于通信技術(shù)����,例如物理信號沿導(dǎo)線從一臺設(shè)備傳輸至另一臺設(shè)備所需的時 間。這種延遲會進一步擴大主時鐘與各從時鐘之間的失

3. 主時鐘設(shè)備與各從時鐘設(shè)備之間的廣播路徑存在差異��,這會進一步降低各從時鐘設(shè)備之間的同步精度�。

IEEE 1588 要求通過測量路徑延遲,解決第二個和第三個問 題��。它還要求待調(diào)整的從時鐘與主時鐘保持步調(diào)一致���,從而減 輕第一個問題����。如果可能,使用更小的廣播間隔和更高質(zhì)量的 振蕩器���,可以進一步減輕第一個問題

IEEE 1588 如何測量通信延遲

IEEE 1588-20022 定義了四種消息 Sync、 Followup�、 DelayReq和 DelayResp,用來測量前向(主時鐘至從時鐘)和后向(從 時鐘至主時鐘)路徑的通信延遲��。更新版本IEEE 1588-2008,3 還提供其它機制��,新增三種消息 PdelayReq��、PdelayResp和PdelayRespFollowup�,來測量"點對點延遲"。

這些消息中�����,Sync����、DelayReq、PdelayReq 和PdelayResp 是所謂"事件"消息���,在離開和到達一臺設(shè)備時必須加上"時間 戳"(記錄本地時間)����。給分組加上時間戳的方法有兩種

1. 消息由軟件處理時出現(xiàn)軟件時間戳。通常出現(xiàn)在消息的接收/發(fā)送"中斷服務(wù)程序"(ISR)中�,該時間戳為系統(tǒng)時間的當前值。

2. 消息實際到達或離開設(shè)備時出現(xiàn)硬件時間戳��。該時間戳操作由硬件執(zhí)行����,硬件會維護自己的連續(xù)時間信息。

兩種時間戳方法均為IEEE 1588 所接受�����,但硬件時間戳的精度明顯更高���,如下文所述�。

主時鐘設(shè)備到從時鐘設(shè)備的延遲

消息Sync 和Followup 由主時鐘設(shè)備發(fā)送����,從時鐘設(shè)備負責接 收這些消息,并計算主時鐘設(shè)備到從時鐘設(shè)備的通信路徑延遲.

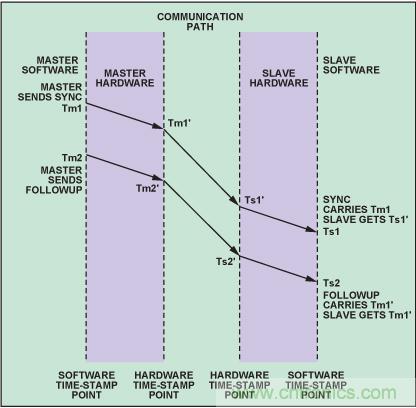

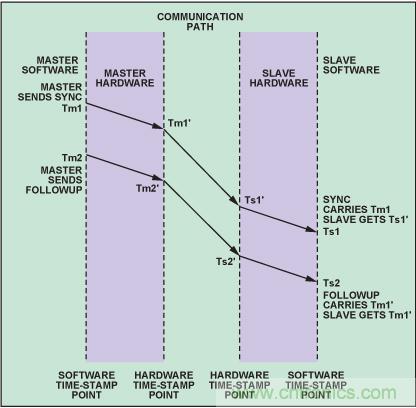

圖2 中�,在時間點 Tm1,主時鐘設(shè)備軟件讀取當前本地系統(tǒng) 時間(Tm1�,軟件時間戳)��,將其插入 Sync 消息中�,并送出 該消息���。該消息在稍 后的時間點 Tm1'''' 離開主時鐘設(shè)備�����,該時 間點為硬件時間戳。該消息在時間點 Ts1'''' (從時鐘設(shè)備本地時間)到達從時鐘硬件�����,從時鐘設(shè)備軟件在稍后的時間點 Ts1 收到該消息����。該軟件將讀取硬件時間戳以獲得 Ts1''''。如果沒有通 信延遲��,Ts1'''' 應(yīng)等于(Tm1'''' + Tms)��,其中 Tms 為主時鐘與從時 鐘之間的時間差��。該協(xié)議的最終目標是補償此時間差.

圖 2. 測量主時鐘設(shè)備與從時鐘設(shè)備之間的通信延遲

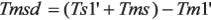

發(fā)送 Sync 消息之后�����,主時鐘設(shè)備軟件通過時間戳單元讀取 Sync 消息的離開時間 Tm1'''' ,將其插入 Followup 消息中��,然后 在時間點 Tm2 發(fā)送該消息����。從時鐘設(shè)備軟件在時間點 Ts2 收 到此消息。此時���,從時鐘設(shè)備軟件有兩個時間: Ts1'''' ( Sync 到 達時間)和 Tm1'''' ( Sync 離開時間)�����。主從路徑延遲 Tmsd 由 公式 1 確定��。

(1)

從時鐘設(shè)備到主時鐘設(shè)備的延遲ce

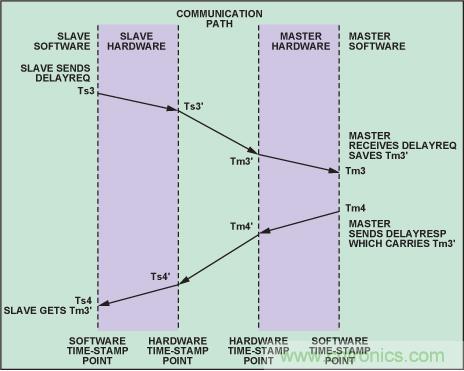

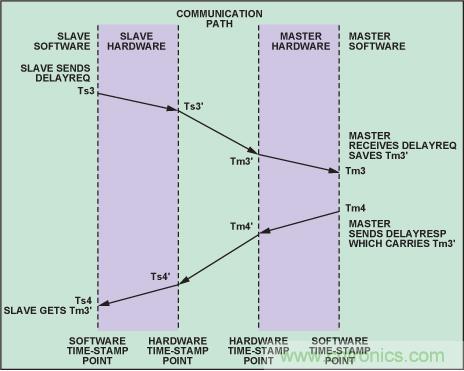

從時鐘設(shè)備發(fā)送 DelayReq 消息�,主時鐘設(shè)備予以響應(yīng)發(fā)送 DelayResp 消息�����。利用這些消息��,從時鐘設(shè)備可以計算從時鐘 設(shè)備到主時鐘設(shè)備的通信路徑延遲.

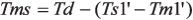

在時間點 Ts3 (圖 3 )����,從時鐘設(shè)備軟件讀取當前本地系統(tǒng)時 間 (T s3) ����,將其插入 DelayReq 消息中�����,并送出該消息�。發(fā)送該 消息之后,從時鐘設(shè)備軟件讀取時間戳以獲取消息離開時間 Ts3'''' ���,并等待主時鐘設(shè)備的響應(yīng)。

圖 3. 測量從主通信延遲

DelayReq 消息在稍后的時間點 Tm3'''' 到達主時鐘設(shè)備�,由主時 鐘設(shè)備軟件在時間點 Tm3 處理。然后�,該軟件讀取時間戳以 獲取到達時間 Tm3'''' ,將其插入 DelayResp 消息中�����,并在時間 點 Tm4 發(fā)送至從時鐘設(shè)備�����。當從時鐘設(shè)備軟件在時間點 Ts4 收到 DelayResp 消息時,它可以提取時間 Tm3'''' �����,并通過公式 2 計算從主通信延遲 Tsmd �����。

(2)

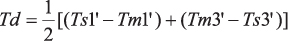

公式 1 和公式 2 中均有一個未知變量��,即主從時間差 Tms ���,因 此無法單獨求得 Tmsd 或 Tsmd ����。但是�����,如果我們合理地假設(shè) 通信路徑是對稱的����,即

(3)

——這是IEEE 1588 成立的關(guān)鍵假設(shè)——那么,將公式1 與公式 2 相加可以得出

(4)

由于從時鐘設(shè)備尋求與主時鐘設(shè)備同步,因此所有這些計算 均由這些設(shè)備執(zhí)行����。從時鐘設(shè)備從主時鐘設(shè)備的 Followup 消 息獲得 Tm1'''' ,從其 Rx (接收)時間戳獲得 Ts1'''' ����,從其 Tx (發(fā) 送)時間戳獲得 Ts3'''' ,并通過主時鐘設(shè)備的 DelayResp 消息獲 得 Tm3''''.

如何計算從時鐘與主時鐘的時間差

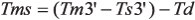

一旦獲得通信路徑延遲 Td �,便可利用公式 1 或公式 2 輕松計 算從時鐘與主時鐘的時間差,如公式 5 和公式 6 所示

(5)

(6)

如何調(diào)整從時鐘設(shè)備的時間

知道與主時鐘的時間差之后�,各從時鐘需要調(diào)整自己的本地時 間,與主時鐘保持一致�。該任務(wù)包括兩方面。第一�����,從時鐘設(shè) 備需要加上時間差以調(diào)整絕對時間�����,使其時間在此刻與主時鐘 時間完全一致��。第二�����,從時鐘設(shè)備需要調(diào)整各自的時鐘頻率��, 與主時鐘的頻率保持一致��。我們不能單靠絕對時間����,因為時間 差僅在一定期間內(nèi)應(yīng)用,可能是正值��,也可能是負值�;調(diào)整的 結(jié)果是從時鐘時間向前跳躍或向后倒退。因此����,在實際操作 中,調(diào)整分兩步執(zhí)行:

1. 如果時間差過大��,例如

2. 如果時間差較小�,則使從時鐘的頻率改變某一百分比.

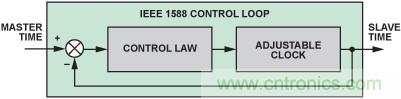

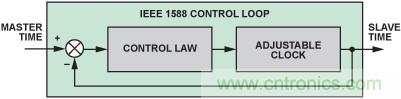

一般而言,該系統(tǒng)會變成一個控制環(huán)路��,其中主時鐘時間是參 考命令��,而從時鐘時間是跟蹤主時鐘時間的輸出,二者之差驅(qū) 動可調(diào)整時鐘����。可以使用 PID 控制來實現(xiàn)特定跟蹤性能��,這 是許多 IEEE 1588 實施方案常用的方法�����。圖 4 顯示了這種控制環(huán)路.

圖 4. IEEE 1588 控制環(huán)路.

點對點延遲

修訂版 IEEE 1588-2008 引入了新的機制來測量路徑延遲����,稱 為"點對點" (P2P) 延遲。與之相比����,上文討論的主從機制則 是"端對端" (E2E) 延遲。在支持 IEEE 1588-2008 的網(wǎng)絡(luò)中����, 主時鐘設(shè)備可以與從時鐘設(shè)備直接相連�,或者隔幾個中繼站 (級)相連。 E2E 延遲實際上是主時鐘設(shè)備到從時鐘設(shè)備的 "總"延遲����,包括其間的所有中繼站在內(nèi)����。但是��, P2P 延遲則 僅限于兩個直接相連的設(shè)備���。通信路徑的總延遲等于所有中繼 站的 P2P 延遲之和�。從確保路徑對稱性的角度看�, P2P 機制可 提供更高的精度.

如上文所述, IEEE 1588-2008 新增了 PdelayReq ����、 PdelayResp 和 PdelayRespFollowup 三種消息來測量 P2P 延遲。這些消息 的工作方式與上文所述方式相似�����,詳情請看參考文獻3�����。

影響同步性能的因素

精心 設(shè)計的 IEEE 1588 設(shè)備能夠?qū)崿F(xiàn)高度精確的時鐘同步����,但 也必須了解直接影響同步性能的主要因素����,其中包括:

1. 路徑延遲: 如上文所述�����, IEEE 1588 的路徑延遲測量假設(shè)通 信路徑延遲是對稱的���,即前向路徑的傳輸延遲與后向傳輸 延遲相同�����。此外�,在延遲測量期間���,延遲不應(yīng)變化�。測量 期間延遲變化會導(dǎo)致不對稱和延遲抖動�,這將直接影響同 步精度。雖然無法在 IEEE 1588 設(shè)備的邊界之外控制延遲對 稱性和抖動�,但如果測量基于硬件時間戳,則可在設(shè)備內(nèi) 改善路徑對稱性和抖動����。由于中斷延時、環(huán)境切換和線程 調(diào)度���,軟件時間戳會導(dǎo)致明顯的抖動��,而硬件時間戳則不

2. 時鐘的漂移和抖動特性:: 主時鐘的頻率和相位代表跟蹤控 制系統(tǒng)的輸入��,從時鐘則是控制對象���。主時鐘的任何時變 行為都會擾動該控制系統(tǒng),導(dǎo)致穩(wěn)態(tài)和瞬態(tài)兩種誤差�����。因

3. 控制法則: 從時鐘調(diào)整如何校正從時鐘設(shè)備的時間誤 差取 決于控制方法��??刂品▌t參數(shù)包括建立時間、過沖和穩(wěn)態(tài)

4. 時鐘分辨率: 如圖 1 所示����,本地時間的分辨率由時鐘頻率 決定;最小時間增量為時鐘信號的一個周期�����。 IEEE 1588- 2002 支持 1 ns 的時間分辨率, IEEE 1588-2008 則支持 2 -16 ns 的時間分辨率�����。 2 16 (!) GHz (甚至 1 GHz )的時鐘是不 現(xiàn)實的���。本地時鐘的量化會影響本地時間測量和控制的精

5. Sync 消息的發(fā)送周期: 從時鐘的更新頻率最終會影響同步 精度��。因為時間誤差是從時鐘頻率誤差的整體累積值����,所 以發(fā)送周期越長����,下一個 Sync 所觀察到的時間誤差一般會

6. 延遲測量的頻率: 以預(yù)期相鄰采樣點之間延遲沒有明顯變 化的間隔時間,定期執(zhí)行延遲測量���。如果 IEEE 1588 網(wǎng)絡(luò) 的延遲變化較大�����,則增加延遲測量頻率可以改善時鐘同步 性能���。

哪個是主時鐘��?

在考慮如何精確確 定主時鐘設(shè)備與從時鐘設(shè)備之間的時間差之 后,下一個相關(guān)問題是:在成百上千臺互連設(shè)備中�����,如何確定 哪一臺設(shè)備充當主時鐘��。

IEEE 1588 定義了一種稱為"最佳主時鐘" (BMC) 算法的方 法�����,用于選擇主時鐘設(shè)備�����。這種方法要求 IEEE 1588 網(wǎng)絡(luò)的每 臺設(shè)備均提供一個數(shù)據(jù)集�����,描述其本地時鐘的性質(zhì)���、質(zhì)量�����、穩(wěn) 定性�����、唯一識別符和首選設(shè)置��。當一臺設(shè)備加入 IEEE 1588 網(wǎng) 絡(luò)時����,它會廣播其時鐘的數(shù)據(jù)集,并接收所有其它設(shè)備的數(shù)據(jù) 集�。利用所有參與設(shè)備的數(shù)據(jù)集,每臺設(shè)備均運行同一 BMC 算法����,以確定主時鐘及其自己的未來狀態(tài)(主時鐘或從時 鐘)。由于所有設(shè)備均采用同樣的數(shù)據(jù)獨立執(zhí)行同一算法�,因 此結(jié)論將會相同,設(shè)備之間不需要進行任何協(xié)商�。有關(guān) BMC 算法的更多詳細信息,請看參考文獻 2 和 3 �。

ADSP -BF51 8 處理器支持 IEEE 1588

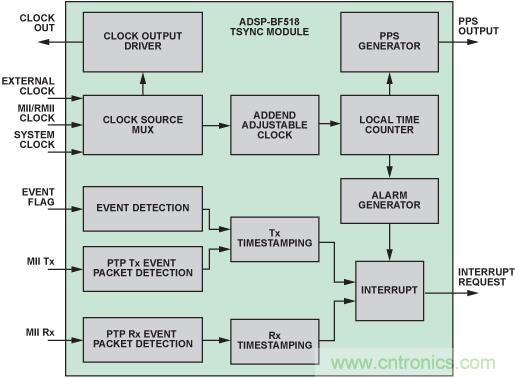

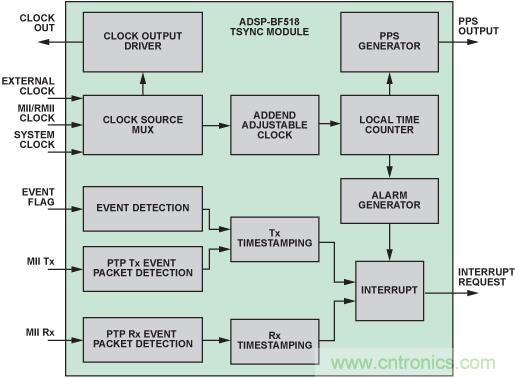

ADI 公司 Black fi n DSP 系列最近新增一款產(chǎn)品: ADSP-BF518 處理器。像前款產(chǎn)品 ADSP-BF537,4 該處理器內(nèi)置"以 太網(wǎng)媒體訪問控制器" (EMAC) 模塊。它還具有 TSYNC 模 塊���,進一步擴展了支持 IEEE 1588 標準 EMAC 功能的能力�����; 還提供其它額外特性�����,可支持以太網(wǎng)的各種 IEEE 1588 應(yīng)用。 圖 5 顯示了 TSYNC 模塊的框圖����。 ADSP-BF51x Blackfin 處理 器硬件參考提供了更多信息5

圖 5. ADSP-BF518 處理器 TSYNC 模塊的框圖。

分組檢測

ADSP-BF518 處理器可以檢測 IEEE 1588 的所有事件消息�,包 括送入和送出的分組,并為其提供硬件時間戳�。因為事件消息 時間戳的精度及其提取位置會影響路徑延遲的對稱性和穩(wěn)定 性要求,所以 IEEE 1588 系統(tǒng)的精度在很大程度上取決于這二 者�����。 ADSP-BF518 的 TSYNC 模塊持續(xù)監(jiān)控 MAC 控制器與以 太網(wǎng)"物理接口收發(fā)器" (PHY) 之間的硬件接口����,即"媒體獨 立接口" (MII) ���,并且只要檢測到事件消息,就會產(chǎn)生硬件時 間戳���,這一功能可提高 ADSP-BF518 的同步精度�。

事件消息檢測功能是可編程的�,基本配置有兩種:支持 IEEE 1588-2002 (默認狀態(tài))或支持 IEEE 1588-2008 。此外�,這種 可編程能力還支持將來版本的 IEEE 1588 ,以及其它要求時間 戳的一般協(xié)議�����,包括配置為給進出處 理器的每個以太網(wǎng)分組加 上時間戳����。

靈活的時鐘源

本地時鐘的屬性對于 IEEE 1588 系統(tǒng)的性能很重要。為了滿足 各種不同應(yīng)用的要求�, ADSP-BF518 處理器可提供三種本地時 鐘源選項:系統(tǒng)時鐘、外部時鐘或以太網(wǎng)時鐘��。如果應(yīng)用具有 特定時鐘要求�����,則可以選擇"外部時鐘",并提供定制時鐘 源��。如果主時鐘設(shè)備與從時鐘設(shè)備"背靠背"連接����,由于"以 太網(wǎng)時鐘"來自以太網(wǎng)線路,而且兩臺設(shè)備采用同一時鐘工 作���,因此該時鐘選項可以提供良好的精度�����。一般應(yīng)用可以選擇 處理器的"系統(tǒng)時鐘"作為時鐘源。

所選源時鐘也由 TSYNC 模塊驅(qū)動�,通過特定引腳 Clockout 作 為處理器輸出,系統(tǒng)的其它部分可利用該輸出提供本地時間信息���。

PPS 輸出

"每秒脈沖" (PPS) 信號是時間信息的物理表示���。它名義上是 一個 1-Hz 信號,在每個 1 秒轉(zhuǎn)換時間發(fā)出一個脈沖��。它可用 來控制本地設(shè)備,或者在發(fā)生網(wǎng)絡(luò)故障時提供輔助時間通道��。 它也可以 用于測試��。兩臺設(shè)備的 PPS 信號之間的相位差是二 者時間偏移的物理量度

ADSP-BF518 處理器提供靈活的 PPS 輸出�����。它利用可編程"開 始時間" (PPS_ST) 和周期 (PPS_P) 產(chǎn)生一個在時間 (PPS_ST + n × PPS_P) 發(fā)出脈沖的信號�����,其中 n = 1, 2, 3 ...���?���;居梅ㄊ?將 PPS_P 設(shè)置為 1 秒���,并將 PPS_ST 設(shè)置為用秒數(shù)表示的將來 任一時刻�,從而產(chǎn)生 PPS 信號����。參考基本用法���,可以利用這 種 PPS 輸出功能產(chǎn)生具有可編程頻率和開始時間的周期性信號。

輔助快照

一些應(yīng)用可能需要按照標志信號切換指示����,給某一事件加上時 間戳。 ADSP-BF518 的 TSYNC 模塊通過輔助"快照" 功能���, 使用一個專用引腳來接收外部標志��,以便實現(xiàn)這種請求����。切換 標志將觸發(fā)該模塊捕捉時間戳寄存器中的當前本地時間���,供軟 件訪問��。.

報警

如果應(yīng)用需在特定時間執(zhí)行一項任務(wù),則可以用 TSYNC 模塊 的"報警"功能���。這項功能可以設(shè)置本地絕對時間��,到達該時 間時��,就會觸發(fā)處理器中斷����。然后,軟件便可利用中斷執(zhí)行任 務(wù)��。

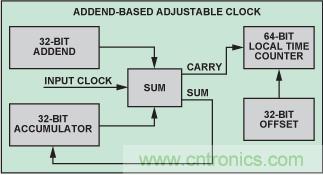

可調(diào)時鐘

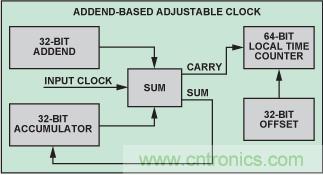

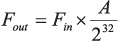

TSYNC 模塊的可調(diào)時鐘是一種"基于加數(shù)"的時鐘�����。如圖 6 所示�����,它獲得一個固定輸入時鐘信號�����,并輸出該輸入的"盜取 脈沖"版本信號:對于每個輸入時鐘����,"加數(shù)"的值增加到累 加器中,并且每次累加器溢出時�����,進位位就會驅(qū)動"本地時間計數(shù)器",從而產(chǎn)生以脈沖計數(shù)值表示的本地時間���。更改加數(shù) 可以調(diào)整本地時鐘的頻率���,因為加數(shù)決定累加器溢出的頻率, 從而決定本地時間計數(shù)器遞增的頻率�。如果輸入時鐘的頻率為 Fin,且加數(shù)的值為A���,則本地時鐘頻率為:

(7)

圖 6. 基于加數(shù)的可調(diào)時鐘

采用ADSP-BF518 處理器的 IEEE 1588 實施方案

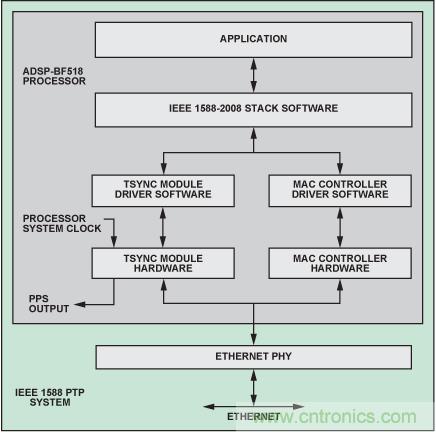

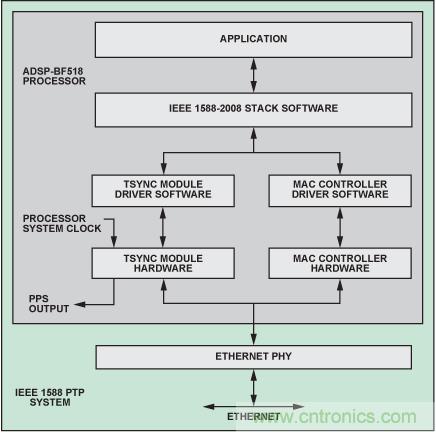

ADSP-BF518 處理器上構(gòu)建了一個完整的 IEEE 1588-2008 兼容系統(tǒng)���,如圖 7 所示。

圖7. 采用ADSP-BF518 的 IEEE 1588 實施方案

處理器的 TSYNC 模塊檢測送入和送出的 IEEE 1588 消息�, 并通過硬件給事件消息加上時間戳。由 I X X AT ( I X X AT Automation GmbH) 提供的 IEEE 1588 協(xié)議棧軟件可實現(xiàn)標準 所要求的消息交換協(xié)議�����。它利用 TSYNC 驅(qū)動程序讀取�����、寫 入并調(diào)整 TSYNC 時鐘��,并使用 MAC 控制器驅(qū)動程序在以太 網(wǎng) MAC 層(開放系統(tǒng)互連模型的第二層)發(fā)送和接收消息����。它還可實現(xiàn) P2P 延遲測量的控制法則和過濾。以太網(wǎng) PHY 選擇具有低抖動延遲特性的 National Semiconductor DP838486����。為簡明起見,TSYNC 模塊時鐘源選擇處理器的系統(tǒng)時鐘 (80 MHz)��。

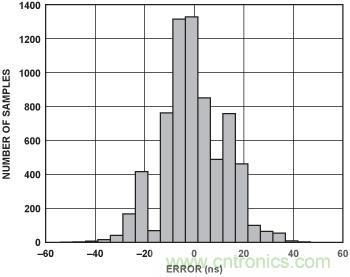

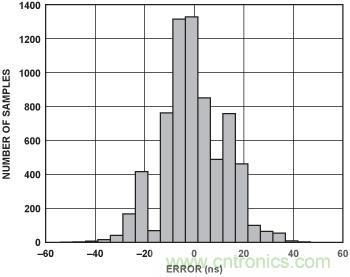

圖 8. ADSP-BF518 上 IEEE 1588 系統(tǒng)的從時鐘誤差直方圖

圖 8 是兩個完全相同的 ADSP-BF518 IEEE 1588 系統(tǒng)之間的 測量誤差直方圖��,由此可看出該器件的時鐘同步性能���。在 約 1700 秒的時間內(nèi)共進行了 6938 次測量����。最終平均誤差為0.015 ns����,標準差為 12.96 ns。該測試所用的 Sync 消息間隔為0.25 秒����。

結(jié)論

IEEE 1588 標準提供了一種高精度�����、低成本的分布式時鐘同步 方法���。雖然 IEEE 1588 并未明文要求硬件支持,但硬件輔助 消息檢測和時間戳對于實現(xiàn)極高同步精度至關(guān)重要��。 ADSP- BF518 為 IEEE 1588-2002 和 IEEE 1588-2008 提供硬件支 持�,包括各種應(yīng)用的支持功能。利用 ADSP-BF518 處理器和 IXXAT IEEE 1588-2008 協(xié)議軟件實施 IEEE 1588 技術(shù)���,已證 明可以實現(xiàn)高精度時鐘同步��。

參考電路

1 ADSP-BF518 數(shù)據(jù)手冊�����。 http://www.analog.com/en/products/processors-dsp/blackfin/adsp-bf518.html.

2IEEE Std. 1588-2002. 網(wǎng)絡(luò)測量和控制系統(tǒng)的精密時鐘同步協(xié) 議 IEEE 標準�����。 http://ieeexplore.ieee.org/stamp/stamp.jsp?arnumber=1048550.

3IEEE Std. 1588-2008. 網(wǎng)絡(luò)測量和控制系統(tǒng)的精密時鐘同步協(xié) 議 IEEE 標準���。http://ieeexplore.ieee.org/stamp/stamp.jsp?arnumber=4579760.

4ADSP-BF537 數(shù)據(jù)手冊����。 http://www.analog.com/en/products/processors-dsp/blackfin/adsp-bf537.html.

5ADSP-BF51x Blackfin 處理器硬件參考�����,0.1 版(初始版)�����。 2009 年 1 月���。 Analog Devices, Inc.http://www.analog.com/media/en/dsp-documentation/processor-manuals/ADSP-BF51x_hwr_rev1.2.pdf.

6AN-1507 :DP83848 和 DP83849 100Mb 數(shù)據(jù)延時。 2006. National Semiconductor Corporation. http://www.ti.com/lit/an/snla084b/snla084b.pdf.

推薦閱讀: