【導(dǎo)讀】隨著近年來工業(yè)互聯(lián)網(wǎng)蓬勃發(fā)展,智能化信息化進(jìn)程逐步加快,而EtherCAT技術(shù)由于其具有通訊的高性能,硬實時性能,靈活的拓?fù)浣Y(jié)構(gòu),簡單、低成本及充分的開放性,以EtherCAT為代表的工業(yè)以太網(wǎng)的發(fā)展勢頭遠(yuǎn)超現(xiàn)場總線,逐漸成為未來工業(yè)互聯(lián)網(wǎng)的主流應(yīng)用。

EtherCAT是使用100Mbit/s 全雙工的Ethernet通訊。通常由EtherCAT從站控制器(EtherCAT Slave Controller,ESC)和物理層接口PHY實現(xiàn)EtherCAT的應(yīng)用。ESC通常會支持PHY使用MII,RMII和RGMII接口,由于RMII和RGMII接口包含TX FIFO,會增加EtherCAT從站設(shè)備的傳輸延時,同時也會引入抖動,所以一般不建議在EtherCAT應(yīng)用中使用,本文主要討論PHY的MII接口的硬件配置。

下圖是ESC和PHY MII之間的連接關(guān)系的示意圖。ESC和PHY之間的時鐘必須保持一致。LINK_STATUS是一個LED輸出信號,用來指示100Mbit/s全雙工的通訊連接狀態(tài)。

圖 1 ESC和MII連接關(guān)系示意圖

下表是使用MII接口的EtherCAT PHY的信號要求以及說明。

DP83822 是一款低功耗單端口10/100Mbps以太網(wǎng)PHY。它提供通過標(biāo)準(zhǔn)雙絞線電纜發(fā)送和接收數(shù)據(jù)或者連接到外部光纖收發(fā)器所需的所有物理層功能。此外,DP83822還可通過標(biāo)準(zhǔn)MII、RMII或RGMII接口靈活地連接到MAC。

DP83822的部分接收路徑功能pin腳可以用bootstrap的方式將PHY配置為特定的工作模式,這些pin腳的電壓值會在上電或者Reset的時候被檢測到,從而完成PHY的配置。DP83822可以通過一個4電平的bootstrap電路來配置,bootstrap pin腳需要增加推薦值的上拉或者下拉電阻來設(shè)置電壓,從而配置為某種特定模式。

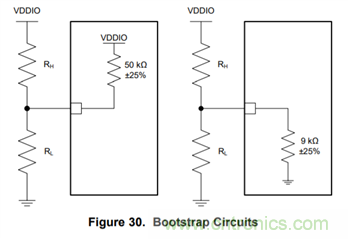

下圖是DP83822的bootstrap電路示意圖,一部分bootstrap pin腳內(nèi)置50kΩ的上拉電路,另一部分的bootstrap pin腳內(nèi)置9kΩ的下拉電阻。通過外加上拉電阻RH和下拉電阻RL可將該bootstrap pin配置為特定模式。

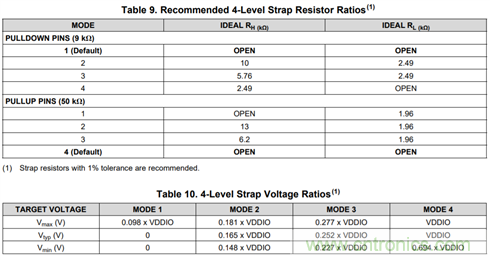

下表是DP83822的四電平配置上拉電阻和下拉電阻的推薦值,結(jié)合該bootstrap pin內(nèi)置的上拉或者下拉電阻,可將該pin配置為四種模式中的一種。

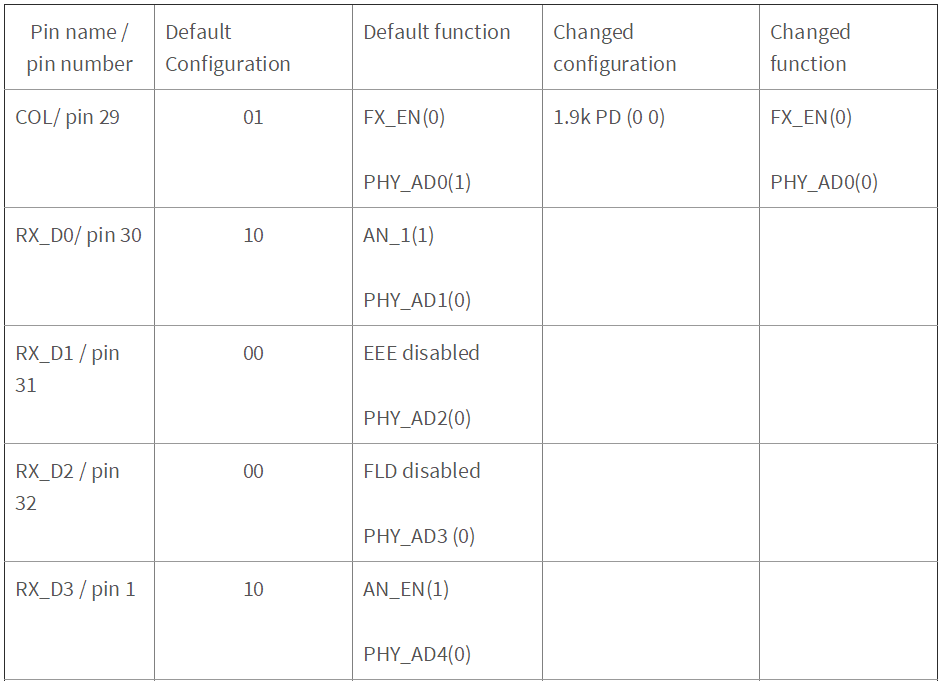

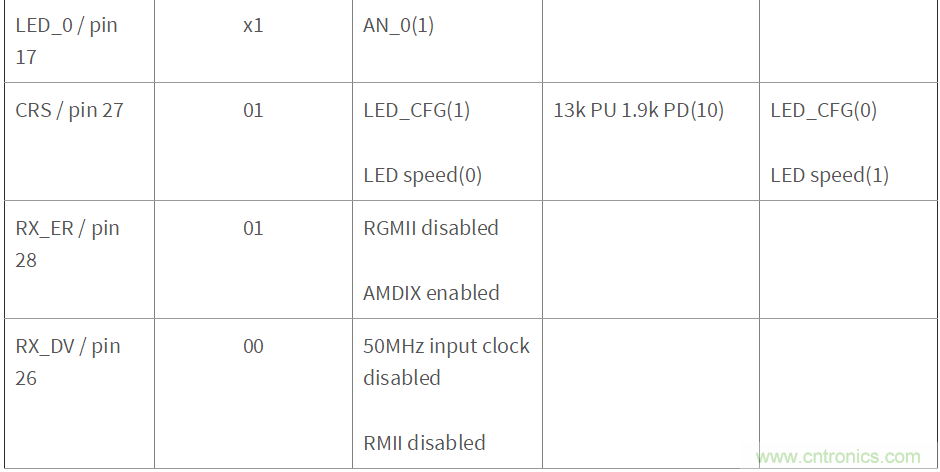

下表是應(yīng)用于EtherCAT MII的DP83822的bootstrap配置示例,配置pin29將地址的最低位PHY_AD0配置為0(作為地址位配置的示例)。此外,配置pin27將LED 0和LED 1配置為EtherCAT應(yīng)用要求的功能。其他bootstrap pin保持默認(rèn)值即可。

FX_EN AN_EN AN_1 AN_0 0 1 1 1 à Advertised Modes, 100BASE-TX and 10BASE-Te, Half and Full-Duplex

LED_SPEED LED_CFG[0] 1 0 à LED 0(Good link/blink activity) LED 1 (show speed (100Mbps/10Mbps)

PHY address 0 0 0 0 0 à serial management interface address 0

DP83826 能夠提供很低的延遲和低功耗,并支持 10BASE-Te、100BASE-TX 以太網(wǎng)協(xié)議,可以滿足實時工業(yè)以太網(wǎng)系統(tǒng)中的嚴(yán)格要求。該器件包含兩種可配置模式:使用通用以太網(wǎng)引腳的 BASIC 標(biāo)準(zhǔn)以太網(wǎng)模式,以及支持標(biāo)準(zhǔn)以太網(wǎng)模式和多個工業(yè)以太網(wǎng)現(xiàn)場總線應(yīng)用的ENHANCED以太網(wǎng)模式。由于在BASIC模式下配置EtherCAT應(yīng)用需要通過軟件對寄存器進(jìn)行寫操作,而ENHANCED模式可完全通過bootstrap pin來完成配置,所以下述主要介紹用ENHANCED模式配置EtherCAT。

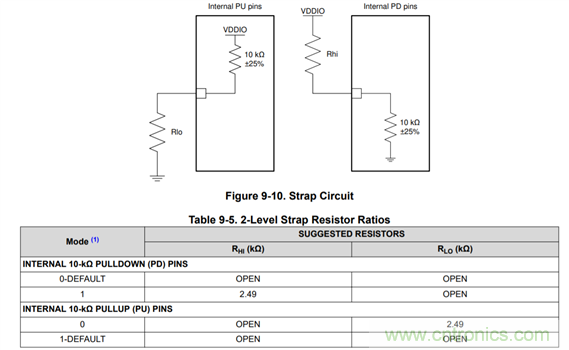

DP83826的bootstrap電路一共由兩個電平,如下圖所示,一部分bootstrap pin腳內(nèi)置10kΩ的上拉電路,另一部分的bootstrap pin腳內(nèi)置10kΩ的下拉電阻。通過外加2.49kΩ的上拉電阻RHI和下拉電阻RLI可將該bootstrap pin配置為特定模式。

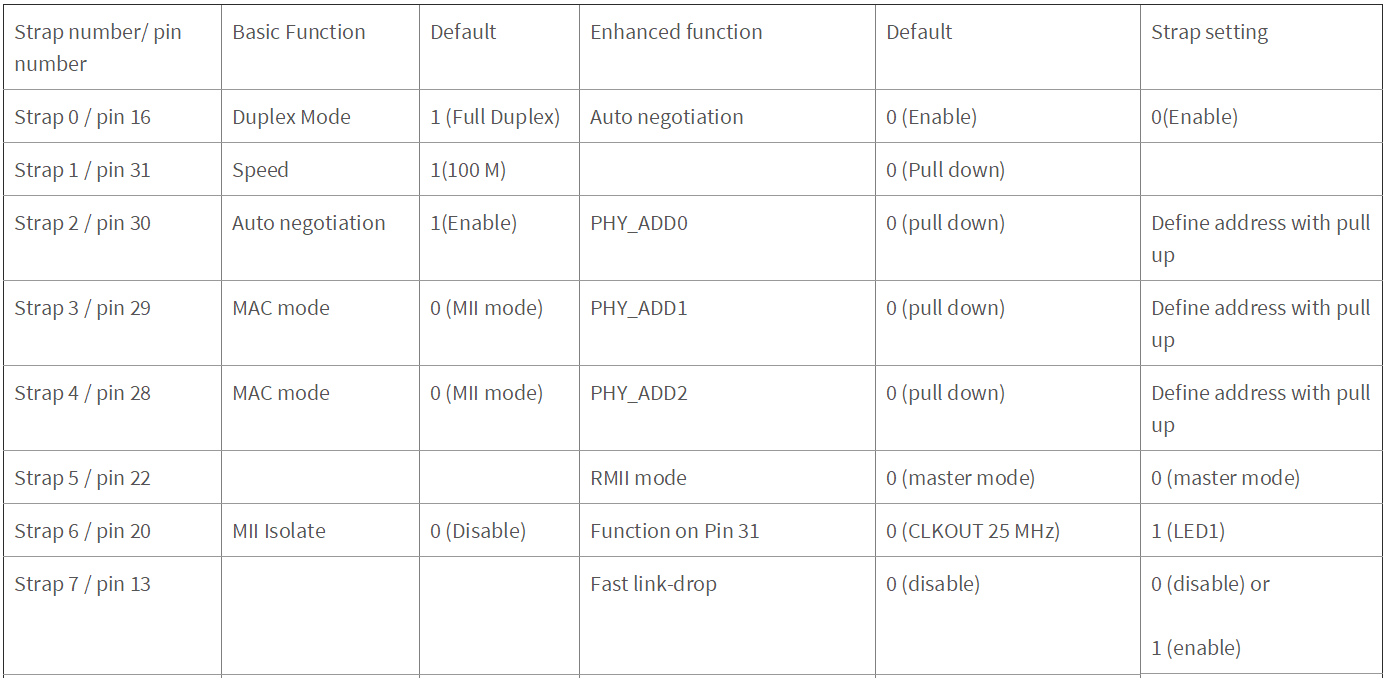

下表是DP83826 bootstrap pin在BASIC和ENHANCED模式下的功能說明,最后一列是配置DP83826為ENHANCED模式下的EtherCAT應(yīng)用。

DP83826也可通過軟件修改寄存器的方式配置為EtherCAT應(yīng)用,具體的細(xì)節(jié)可參考下述技術(shù)文章。

https://www.ti.com/lit/an/snla344/snla344.pdf

TI為工業(yè)互聯(lián)網(wǎng)EtherCAT提供了多種解決方案,可以通過簡單的硬件配置完成EtherCAT應(yīng)用。

參考鏈接:

DP83822數(shù)據(jù)手冊: https://www.ti.com/lit/ds/symlink/DP83822i.pdf

DP83826數(shù)據(jù)手冊: https://www.ti.com/lit/ds/symlink/DP83826i.pdf

Backoff PHY選型應(yīng)用手冊:https://download.beckhoff.com/download/document/io/ethercat-development-products/an_phy_selection_guidev2.7.pdf

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請聯(lián)系小編進(jìn)行處理。

推薦閱讀:

寬禁帶生態(tài)系統(tǒng):快速開關(guān)和顛覆性的仿真環(huán)境 – 第二部分