【導(dǎo)讀】電磁兼容性(EMC)常是制約設(shè)備間匹配性和正常性能實現(xiàn)的重要因素,因此電磁兼容性設(shè)計也是航天器設(shè)計中要考慮的關(guān)鍵因素。文章主要介紹了電磁干擾的產(chǎn)生原因,并從合理布局與布線、電容的設(shè)計、邏輯電路的使用等方面論述了如何在印制電路板(PCB)設(shè)計過程中減少電磁干擾。

1 引言

電磁兼容性(Electromagnetic Compatibility,EMC)是指“一種器件、設(shè)備或系統(tǒng)的性能,它可以使其在自身環(huán)境下正常工作并且不會對此環(huán)境中任何其他設(shè)備產(chǎn)生強烈電磁干擾(IEEEC 63.12-1987)”。對于無線接收設(shè)備來說,采用非連續(xù)頻譜可部分實現(xiàn)EMC性能,但很多例子也表明EMC并不是總能做到。例如在電腦和測試設(shè)備之間、打印機和臺式電腦間、蜂窩電話和醫(yī)療儀器之間等都具有高頻干擾,我們把這種干擾稱為電磁干擾(Elec-tromagnetic Interference,EMI)。電磁干擾是指那些不希望產(chǎn)生的、影響器件或系統(tǒng)正常工作的雜波信號 。

。

所有電器和電子設(shè)備工作時都會有間歇或連續(xù)性的電壓或電流變化,有時變化速率還相當快,這樣

會導(dǎo)致在不同頻率內(nèi)或頻帶間產(chǎn)生電磁能量,而相應(yīng)的電路則會將這種能量發(fā)射到周圍的環(huán)境中。

EMI有兩條途徑離開或進入一個電路:輻射和傳導(dǎo)。信號輻射是通過外殼的縫、槽、開孔或其他缺口泄漏出去;傳導(dǎo)則通過耦合到電源、信號和控制線上離開外殼,在開放的空間中自由輻射,從而產(chǎn)生干擾。

形成EMI必須具備三個基本要素:

(1)傳導(dǎo)或輻射的電磁干擾源;

(2)耦合路徑;

(3)敏感部件(設(shè)備)。

例如在印制電路板(Printed Circuit Board,PCB)中,電磁干擾源于頻率發(fā)生電路、塑料封裝元件等的電磁輻射、地線反彈噪聲、過長傳輸線及電纜互聯(lián)等;耦合路徑為能夠傳輸射頻(Radio Frequen-cy,RF)能量的介質(zhì);如自由空間或金屬互聯(lián)等;敏感部件指能夠接收RF干擾信號的器件。

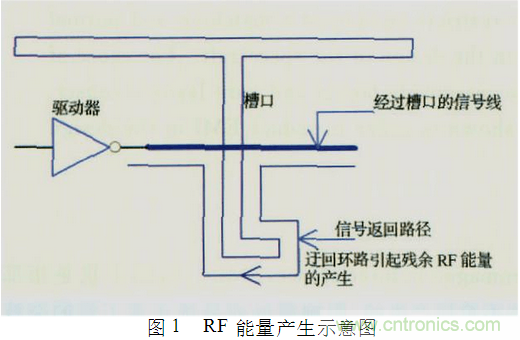

2 PCB中存在電磁干擾的原因

根據(jù)電磁場的基本理論,當外部傳輸線或PCB印制線中存在有RF電流時,電流從電流源流到負載后,必須通過返回路徑返回到電流源,這樣形成了閉合電流環(huán)路,便會產(chǎn)生磁場,該磁場同時又會產(chǎn)生一個輻射電場。這樣,通過電磁場的交互作用實現(xiàn)了RF能量的產(chǎn)生與傳播。因為PCB印制線與RF電流返回路徑間存在有一定的物理距離,磁場與返回結(jié)構(gòu)間的磁通耦合將只能接近而不能達到100%,這種一定量的未被耦合到返回結(jié)構(gòu)的殘余RF電流是PCB中引起電磁干擾的主要原因,如圖1所示。

印制電路板中的電磁干擾問題包括公共阻抗耦合和串擾,高頻載流導(dǎo)線產(chǎn)生的輻射,印制線條對高頻輻射的感應(yīng)等。其中以高頻輻射問題最為嚴重,這是因為電源線、接地線及信號線的阻抗會隨著頻率的增高而增大,故較易通過公共阻抗耦合產(chǎn)生干擾,同時頻率增高使得線路間寄生電容的容抗減小,因而串擾更易發(fā)生。當模擬電路和數(shù)字電路在同一塊印制電路板上混裝時,若電源與地線共用,則可能產(chǎn)生嚴重的公共阻抗耦合問題,在地線回路中產(chǎn)生的干擾電壓,嚴重時可能高于接在公共回路中的模擬和數(shù)字電路的噪音容限,而造成設(shè)備工作的不穩(wěn)定 。

。

3 PCB的EMC設(shè)計

3.1 合理布局與布線

在設(shè)備內(nèi)部,布局或布線不當是造成干擾的首要原因,大多數(shù)的干擾是發(fā)生在模擬數(shù)字混排的布局網(wǎng)或布線不當?shù)挠≈凭€之間。所以正確的布局和布線是設(shè)備可靠運行的基本保證之一。線間耦合不外乎是低頻磁場的電感耦合和高電壓下的電容耦合,線間距離越近,則線間的互感和靜電容就越大。對于磁場耦合來說,兩電路間的耦合情況與干擾信號的頻率、線路上流動的電流、線路間的距離、線路和地間的距離、耦合路徑的長度以及屏蔽層的接地方式有關(guān)。對電容耦合來說,電路間的耦合情況同樣也與干擾信號的頻率、線間距離、屏蔽情況、線路上的電壓高低等因素有關(guān)。因此,合理布局和布線是PCB的EMC設(shè)計的關(guān)鍵,下面提出具體的設(shè)計方案。

當高速、中速和低速數(shù)字電路混用時,在印制板上要給它們分配不同的布局區(qū)域。對低電平模擬電路和數(shù)字邏輯電路要盡可能地分離。因為這種布局可以使高頻電流在印制板上的走線路徑變短,有助于降低線路板內(nèi)部的串擾、公共阻抗耦合和輻射發(fā)射。元器件的布局首先要考慮的一個因素就是電性能,把連線關(guān)系密切的元器件盡量放在一起,高速線走線盡可能短。功率信號和小信號器件要分開,這樣可減少組件之間的電磁干擾。

信號線上的傳輸時間對總的系統(tǒng)速度影響很大,特別是對高速的發(fā)射極耦合邏輯(Emitter-Cou-pled Logic,ECL)電路,雖然集成電路塊本身速度很高,但由于在底板上用普通的互連線(每30cm線長約有2ns的延遲量)帶來延遲時間的增加,可使系統(tǒng)速度大為降低,并可能導(dǎo)致同步時序錯誤。所以在系統(tǒng)布局時最好將同步工作部件放在同一塊插件板上,因為到不同插件板上的時鐘信號的傳輸延遲時間不相等,可能使移位寄存器產(chǎn)生錯誤邏輯;若不能放在一塊板上,也要盡可能保證公共時鐘源連到各插件板的時鐘線的長度相等。

較好的印制電路板布線方案是讓模擬和數(shù)字電路分別擁有自己的電源和地線通路,這樣干擾電壓就不會出現(xiàn)在電路的輸入端上。在可能的情況下加寬電路的電源與地線,以減小電源與地線回路的阻抗,減小任何可能在電源與地線回路中的干擾電壓。

進行多層印制板設(shè)計時,首先要考慮的是帶寬。數(shù)字電路的EMC設(shè)計中要考慮的是數(shù)字脈沖的上升沿和下降沿所決定的頻帶寬而不是數(shù)字脈沖的重復(fù)頻率。矩形的周期數(shù)字脈沖的傅立葉展開見公式(1)。

式中: 是數(shù)字脈沖寬度,

是數(shù)字脈沖寬度, 是數(shù)字脈沖的上升時間,T是數(shù)字信號的重復(fù)周期,A是信號幅值。根據(jù)這個結(jié)果可以把方形數(shù)字信號的印制板設(shè)計帶寬定為

是數(shù)字脈沖的上升時間,T是數(shù)字信號的重復(fù)周期,A是信號幅值。根據(jù)這個結(jié)果可以把方形數(shù)字信號的印制板設(shè)計帶寬定為 ,通常要考慮這個帶寬的10倍頻。所以在選擇邏輯器件時,要選上升時間比5ns長的器件,不要選擇比電路要求時序快的邏輯器件。而對于速度較快的邏輯電路,特別是超高速ECL集成電路來說,因其邊沿速度增快,故走線的長度必須大大縮短以保持信號完整性。

,通常要考慮這個帶寬的10倍頻。所以在選擇邏輯器件時,要選上升時間比5ns長的器件,不要選擇比電路要求時序快的邏輯器件。而對于速度較快的邏輯電路,特別是超高速ECL集成電路來說,因其邊沿速度增快,故走線的長度必須大大縮短以保持信號完整性。

根據(jù)克?;舴蚨桑魏螘r域信號由源到負載的傳輸都必須構(gòu)成一個完整的回路,一個頻域信號由源到負載的傳輸都必須有一個最低阻抗的路徑。如果高頻輻射電流不是經(jīng)由設(shè)計中的回路到達目的負載,就一定是通過某個客觀存在電回路到達的,這一非正常回路中的一些器件就會遭受電磁干擾。在數(shù)字電路設(shè)計中,不能忽略的是存在于器件、導(dǎo)線、印制線和插頭上的寄生電感、電容和導(dǎo)納。為此有以下幾條布線的共同原則:

(1)所有平行信號線之間要盡量留有較大的間隔,以減少串擾。如果有兩條相距較近的信號線,最好在兩線之間走一條接地線,可以起到屏蔽作用。設(shè)計信號傳輸線時要避免急拐彎,以防傳輸線特性阻抗的突變而產(chǎn)生反射和振鈴,要盡量設(shè)計成具有一定尺寸的均勻的圓弧線。

(2)印制板上若裝有大電流器件,如繼電器、指示燈、喇叭等,它們的地線最好單獨走線,以減少地線上的噪聲,這些大電流器件的地線應(yīng)連到插件板或背板上的獨立的地總線上去。如果板上有小信號放大器,則放大前的弱信號線要遠離強信號線,而且走線要盡可能短,如有可能還要用地線對其進行屏蔽。時鐘電路和高頻電路是主要的干擾源和輻射源,要單獨安排并遠離敏感電路。

(3)電源平面應(yīng)靠近接地平面,并且安排在接地平面之下。這樣可以利用兩金屬平板間的電容作電源的平滑電容,同時接地平面還對電源平面上分布的輻射電流起到屏蔽作用。

(4)把數(shù)字電路和模擬電路分開,有條件時將數(shù)字電路和模擬電路安排在不同層內(nèi)。如果一定要安排在同一層,可采用開溝、加接地線條、分隔等方法補救,保證模擬和數(shù)字電路的相對獨立性。低速、中

速、高速邏輯電路應(yīng)分區(qū)布設(shè)。

(5)要特別注意電流流過電路中的導(dǎo)線環(huán)路尺寸,因為這些回路就相當于正在工作中的小天線,隨時隨地向空間進行輻射。特別是要注意時鐘部分的走線,因為這部分是整個電路中工作頻率最高的,晶振要盡量靠近集成電路(IC),且布線要較粗,晶振外殼要接地。

3.2 接地設(shè)計

印制板接地方案是印制板EMC設(shè)計的另一個基本的重要問題。RF電流從負載返回電流源途中必須流經(jīng)一個零電位參考結(jié)構(gòu),一般為地線或接地層,這種返回電流途經(jīng)的電位恒定的平面路徑通常稱為參考平面。參考平面的布置有利于多層PCB的磁通消除,但被分割的平面由于形成電流環(huán)路,不能做為優(yōu)化的返回平面去除RF電流。為了利用參考平面實現(xiàn)磁通消除的目的,必須使較大的頻譜能量流經(jīng)的網(wǎng)絡(luò)緊鄰實際RF返回平面,最好是零電位層。接地層最好在電源層之上,因為各種邏輯器件的上拉/下拉電流比例可能很不對稱。其信號磁通相位的移動、較大的線感抗、較差的阻抗控制和噪聲不穩(wěn)定性等使這些開關(guān)器件可能不能形成優(yōu)化的磁通消除條件,所以建立接地平面可以充分分流開關(guān)電流。

建立分布參數(shù)的概念,高于一定頻率時,任何金屬導(dǎo)線都要看成是由電阻、電感構(gòu)成的器件。所以接地引線具有一定的阻抗并且構(gòu)成電氣回路,不管是采用單點接地還是多點接地,都必須構(gòu)成低阻抗回路進入真正的大地或機架。

接地電流流經(jīng)接地線時,會產(chǎn)生傳輸線效應(yīng)和天線效應(yīng)。當線條長度為1/4波長時,可以表現(xiàn)出很高的阻抗,接地線實際上是開路的,接地線反而成為向外輻射的天線,最后接地板上充滿高頻電流和干擾場形成的渦流。因此在接地點之間構(gòu)成許多回路,這些回路的直徑(或接地點間距)應(yīng)小于最高頻率波長的1/20??蓪l(fā)射干擾較少的電路放置到離地點最遠處,將發(fā)射干擾較多的電路放置離匯流地點最近的地方,這樣可通過限制噪聲電路回線阻抗限制公共阻抗的耦合。

3.3 電容的設(shè)計

電容在PCB設(shè)計中有多種功能,如減少地線反彈噪聲、分流功能區(qū)域以及消除電路中共模和差模RF電路等。電容可分為去耦電容、旁路電容和容納電容三類。去耦電容能有效消除由高頻開關(guān)部件產(chǎn)生的RF能量,為部件提供局部的低阻抗直流電壓源,有利于減少通過PCB傳送的電流脈沖峰值。旁路電容能消除高頻輻射噪聲,該噪聲會限制電路帶寬產(chǎn)主共模干擾。容納電容是用來解決開關(guān)器件工作時電源電壓會產(chǎn)生突降的問題。

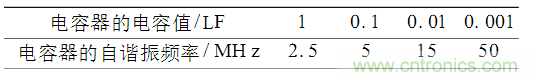

去耦電容可有效抑制電源分布系統(tǒng)的雜波信號。開關(guān)邏輯器件必須使用去耦電容,因為邏輯器件產(chǎn)生的開關(guān)能量脈沖會注入電源分布系統(tǒng)中,會通過共模和差模雜波信號的形式傳輸?shù)狡渌壿嬰娐坊蜃訁^(qū)域中。設(shè)計中需計算去耦電容值以抑制所有的主要時鐘諧波。電容的自諧振頻率應(yīng)高于所有需要抑制的時鐘諧波頻率,因為當需抑制的頻率超過電容自諧頻率時,電容就變成為感性器件從而失去其去耦功能。一些標準電容的自諧頻率參見表1。

表1 電容器的自諧振頻率

去耦電容的電容量按公式(2)計算。

式中$I為瞬變電流,$V為邏輯器件工作允許的電源電壓值的變化,$t為開關(guān)時間。

旁路電容可以轉(zhuǎn)移輸入/輸出(I/O)電纜中的共模電流。

旁路電容可以轉(zhuǎn)移輸入/輸出(I/O)電纜中的共模電流。

旁路電容一般是通過建立與機殼接地的短路將屏蔽電纜中的RF共模電流安全轉(zhuǎn)移的電容(RF電流是交流電流)。旁路電容必須布置在附于PCB板上的I/O互連區(qū)。如果電纜沒有固定在機殼上,就需要采用旁路電容去除屏蔽電纜中的共模電流,以免這種共模電流輻射到自由空間或干擾機殼接地。應(yīng)使用最短的器件接腳并應(yīng)考慮適當?shù)膸挒V波和靜電放電(Electrostatic Discharge,ESD)保護功能。

在電源引線比較長時,瞬變電流引起較大的壓降,就要加容納電容以便維持器件要求的電壓值。

3.4 邏輯電路的使用

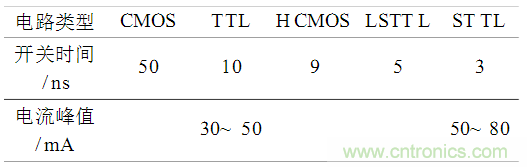

當邏輯門電路輸入條件變化、電路發(fā)生逆轉(zhuǎn)的瞬間,會在門電路的電源和地之間出現(xiàn)一個非常短暫的低阻抗連接,產(chǎn)生非常短暫的電流峰。電流峰的持續(xù)時間與電路的開關(guān)時間大體相等。常見電路的開關(guān)時間與峰值見表2。

表2 常見電路的開關(guān)時間與峰值

注:

CMOS——互補型金屬-氧化物-半導(dǎo)體集成電路(Comple-mentary Metal-Oxide-Semiconductor);

TTL——晶體管邏輯電路(Transistor-Transistor Logic);

HCMOS——高密度互補型金屬-氧化物-半導(dǎo)體集成電路;

LSTTL——低功耗肖特基系列晶體管邏輯電路;

STTL——肖特基系列。

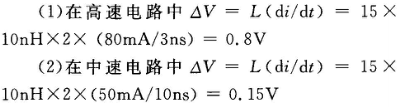

通常細長的印刷導(dǎo)線的分布電感為15LH/cm,對2cm長的印刷導(dǎo)線因門電路邏輯狀態(tài)變化在電源線(或地線)中造成的電壓變化:

可以看出,高速電路工作時產(chǎn)生的電源線或地線干擾要明顯大于低速電路,故從抗干擾和穩(wěn)定運行的角度看,能不用高速邏輯電路的地方就不要用高速邏輯電路。

有兩種方法能使高速電路在相對長的線上工作而無嚴重的波形失真,對晶體管邏輯電路(Tran-sistor-Transistor Logic,TTL)快速下降邊沿采用肖特基二極管箝位方法,使過沖量被箝制在比地電位低一個二極管壓降的電平上,這就減少了后面的反沖幅度。對異質(zhì)結(jié)構(gòu)互補型晶體管(Heterostruc-ture-Coupled Transistor,HCT)系列的器件,若采用肖特基二極管箝位和串聯(lián)電阻端接方法相結(jié)合,其改善的效果將會更加明顯。當沿信號線有扇出時,在較高的位速率和較快的邊沿速率下,上述介紹的TTL整形方法有些不足,因為線中存在著反射波,它們在高位速率下將趨于合成,從而引起信號嚴重失真和抗干擾能力降低。為了解決反射問題,在ECL系統(tǒng)中通常使用另外一種方法:線阻抗匹配法。線阻抗匹配法是指使用傳輸線或在線上加匹配電阻,達到能預(yù)測連線時延和通過阻抗匹配來控制反射和振蕩目的的方法。線路中是否加匹配電阻要視傳輸線的長度來定,對高速電路,在傳輸線達到20~25cm時就要考慮加匹配電阻。匹配電阻的實施有2種模式:

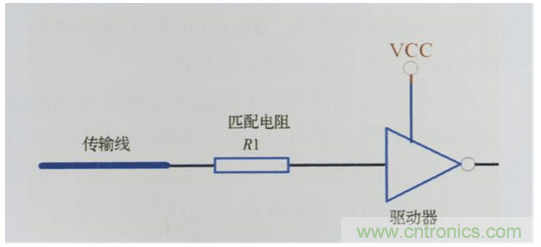

(1)在一條線的接收端用一個與線特性阻抗相等的電阻端接,則稱該傳輸線為并聯(lián)端接線。它主要是為了獲得最好的電性能、驅(qū)動分布負載而采用的。如圖2所示。

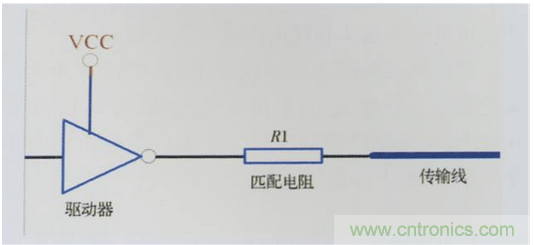

(2)在驅(qū)動器和傳輸線之間串接一個電阻,而線的終端不再接端接電阻,這種端接方法稱之為串聯(lián)端接。較長線上的過沖和振鈴可用串聯(lián)端接技術(shù)來控制。串聯(lián)端接時串聯(lián)電阻的值與電路(驅(qū)動門)輸出阻抗之和等于傳輸線的特性阻抗 ,如圖3所示。

,如圖3所示。

圖2 并聯(lián)端接示意圖

圖3 串聯(lián)端接示意圖

如果線延遲時間比信號上升時間短得多,也可在不用串聯(lián)或并聯(lián)端接的情況下使用傳輸線。并聯(lián)端接線和串聯(lián)端接線都各有優(yōu)點,使用哪一種由系統(tǒng)的要求而定。一般來說,并聯(lián)端接線的主要優(yōu)點是系統(tǒng)速度快且信號在線上傳輸完整無失真。長線上的負載既不會影響驅(qū)動長線的驅(qū)動門的傳輸延遲時間,又不會影響它的信號邊沿速度,但將使信號的傳輸延遲時間增大。串聯(lián)端接方法使電路有驅(qū)動幾條平行負載線的能力,串聯(lián)端接線由于容性負載所引起的延遲時間增量約比相應(yīng)并聯(lián)端接線的大一倍,而短線則因容性負載使邊沿速度放慢以及驅(qū)動門延遲時間增大,但是串聯(lián)端接線的串擾比并聯(lián)端接線的要小,其主要原因是沿串聯(lián)端接線傳送的信號幅度僅僅是1/2的邏輯擺幅,因而開關(guān)電流也只有并聯(lián)端接的開關(guān)電流的一半,信號能量小所以串擾也就小。

4 結(jié)論

PCB的電磁兼容設(shè)計的關(guān)鍵在于如何減少輻射能力以及如何提高抗干擾能力,合理的布局與布線是設(shè)計射頻電路PCB的保證。文中所述方法有利于提高射頻電路PCB設(shè)計的可靠性,解決好電磁干擾問題,進而達到電磁兼容的目的。

參考文獻

[1]陳窮.電磁兼容性工程設(shè)計手冊[M].北京:國防工業(yè)出版社,1993

[2]張松春.電子控制設(shè)備抗干擾技術(shù)及其應(yīng)用[M].北京:機械工業(yè)出版社,1998

[3]韓魁選.微波統(tǒng)一測控系統(tǒng)導(dǎo)論[M].北京:國防工業(yè)出版社,1965

[4]譚博學.集成電路原理及應(yīng)用[M].北京:電子工業(yè)出版社,2003

推薦閱讀: